# Proceedings of the 6th International Workshop on Worst-Case Execution Time Analysis (WCET'06)

Chair: Frank Mueller North Carolina State University, USA

Dresden, Germany, July 4, 2006

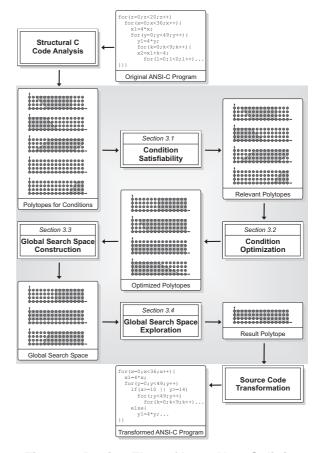

# **Preface**

On the 4th of July, 2006, the 6th International Workshop on Worst-Case Execution Time Analysis (WCET'06) was held in Dresden, Germany, co-located with the 18th Euromicro International Conference on Real-Time Systems (ECRTS'06), both with support of Euromicro Technical Committee. The goal of the workshop is to bring together people from academia, tool vendors and users in industry that are interested in all aspects of timing analysis for real-time systems. The workshop will provide a relaxed forum to present and discuss new ideas, new research directions, and to review current trends in this area. The workshop will be based on short presentations that should encourage discussion by the attendees.

The topics of the workshop include any issue related to timing analysis, in particular:

- Different approaches at computing WCET

- Flow analysis for WCET

- Low-level timing analysis, modeling and analysis of features

- Calculation methods for WCET

- Strategies to reduce the complexity of WCET analysis

- Integration of WCET and schedulability analysis

- Evaluation and case studies

- Testing Methods for WCET analysis

- Tools for timing analysis

- Design for Timing Predictability

- Integration of WCET analysis into the development process

- Compiler optimizations for worst-case paths

- WCET analysis for multi-processors, multi-cores or SMTs

- WCET analysis for networks (e.g., CAN)

WCET'06 featured one invited talk, one report of an upcoming WCET tool contest and, most of all, presentations of technical paper combined with discussions with the attendees. The papers were selected based on peer reviews by program committee members and outside reviewers, all experts in the field.

# Acknowledgments

The workshop chair would like to acknowledge the following people:

- the invited speaker, Tullio Vardanega, Univ. of Padua (Italy), for his voluntary contribution to the workshop;

- Herman Härtig for his local support;

- the WCET SC for their advice;

- and last but not least the eager members of the program committee and the anonymous external reviewers.

|     |            | •   |

|-----|------------|-----|

| The | <i>i</i> h | 211 |

| The | $\sim$ 11  | au, |

Frank Mueller

June 2006

# **WCET'06 Program Committee**

- Henk Corporaal, TU/e (Eindhoven University of Technology). Netherlands.

- Niklas Holsti, Tidorum Ltd.. Finland.

- Björn Lisper, University of Mälardalen. Sweden.

- Stefan Petters, National ICT Australia Ltd. Australia.

- Isabelle Puaut, IRISA Rennes. France.

- Jan Staschulat, University of Braunschweig. Germany.

- Gerhard Unterweger, Consultant for Automotive Industry. Germany.

# **WCET'06 Steering Committee**

- Guillem Bernat, University of York. England, UK.

- Jan Gustafsson, Mälardalen University, Sweden.

- Peter Puschner, Technical University of Vienna, Austria.

# **Table of Contents**

# **Session 1: Tightening WCET Bounds**

Algorithms for Infeasible Path Calculation, Jan Gustafsson, Andreas Ermedahl, and Björn Lisper

Comparing WCET and Resource Demands of Trigonometric Functions Implemented as Iterative Calculations vs. Table-Lookup, Raimund Kirner, Markus Groessing, Peter Puschner

History-based Schemes and Implicit Path Enumeration, Claire Burguière and Christine Rochange

# **Session 2: Timing Anomalies**

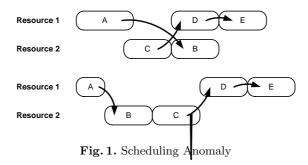

A Definition and Classification of Timing Anomalies, Jan Reineke, Bjoern Wachter, Stephan Thesing, Reinhard Wilhelm, Ilia Polian, Jochen Eisinger, and Bernd Becker

PLRU Cache Domino Effects, Christoph Berg

# **Session 3: Compilers and WCET**

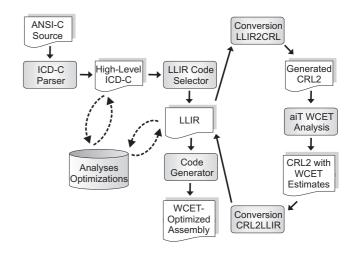

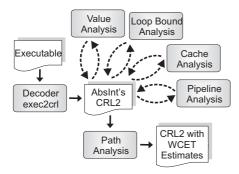

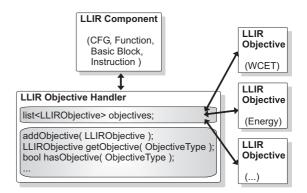

Design of a WCET-Aware C Compiler, Heiko Falk, Paul Lokuciejewski, Henrik Theiling

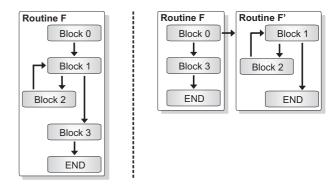

Loop Nest Splitting for WCET-Optimization and Predictability Improvement, Heiko Falk, Martin Schwarzer

Combining Symbolic Execution and Path Enumeration in Worst-Case Execution Time Analysis, D. Kebbal and P. Sainrat

# Session 4: Potpourri

A Framework for Response Times Calculation Of Multiple Correlated Events, Simon Schliecker, Matthias Ivers, Jan Staschulat, Rolf Ernst

Towards Formally Verifiable WCET Analysis for a Functional Programming Language, Kevin Hammond, Roy Dyckhoff, Christian Ferdinand, Reinhold Heckmann, Martin Hofmann, Steffen Jost, Hans-Wolfgang Loidl, Greg Michaelson, Robert Pointon, Norman Scaife, Jocelyn Serot and Andy Wallace

PapaBench: a Free Real-Time Benchmark, F. Nemer, H. Cassé, P. Sainrat, J.P. Bahsoun

# Algorithms for Infeasible Path Calculation

Jan Gustafsson, Andreas Ermedahl, and Björn Lisper Department of Computer Science and Electronics, Mälardalen University Box 883, S-721 23 Västerås, Sweden

{jan.gustafsson, andreas.ermedahl, bjorn.lisper}@mdh.se

# Abstract

Static Worst-Case Execution Time (WCET) analysis is a technique to derive upper bounds for the execution times of programs. Such bounds are crucial when designing and verifying real-time systems. A key component in static WCET analysis is to derive flow information, such as loop bounds and infeasible paths.

Such flow information can be provided as either as annotations by the user, can be automatically calculated by a flow analysis, or by a combination of both. To make the analysis as simple, automatic and safe as possible, this flow information should be calculated automatically with no or very limited user interaction.

In this paper we present three novel algorithms to calculate infeasible paths. The algorithms are all designed to be simple and efficient, both in terms of generated flow facts and in analysis running time. The algorithms have been implemented and tested for a set of WCET benchmarks programs.

# 1 Introduction

To give timing guarantees for embedded and realtime systems, a key parameter is the *worst-case exe*cution time (WCET) of the software. A static WCET analysis analysis finds an upper bound to the WCET of a program, relying on mathematical models of the software and hardware involved. Given that the models are correct, the analysis will derive a timing estimate that is safe, i.e., greater than or equal to the WCET.

To statically derive a timing bound for a program, information on both the hardware timing characteristics, such as the execution time of individual instructions, as well as the program's possible execution flows, to bound the number of times the instructions can be executed, needs to be derived. The latter includes information about the maximum number of times loops are iterated, which paths through the program that are feasible, execution frequencies of code parts, etc.

The goal of *flow analysis* is to calculate such *flow information* as automatically as possible. Flow analysis research has mostly focused on *loop bound* analysis, since upper bounds on the number of loop iterations must be known in order to derive WCET estimates [8].

Flow analysis can also identify *infeasible paths*, i.e., paths which are executable according to the control-flow graph structure, but not feasible when considering the semantics of the program and the possible inputs. Information on infeasible paths is not necessary to find a WCET estimate, but may tighten it.

This article presents ongoing work to automatically calculate infeasible paths. Three new and complementary algorithms are presented. They have been implemented in our prototype WCET analysis tool and tested for a set of WCET benchmarks programs.

The concrete contributions of this article are:

- We present ongoing work to extend our flow analysis method, called *abstract execution*, to calculate information about infeasible paths.

- We present three algorithms, calculating different types of infeasible path information, allowing us to trade analysis time for flow information precision.

- We show how to make our infeasible path algorithms input data dependent, allowing us to calculate more precise flow information for a program with limitations on its possible input data values.

- We evaluate the effect of our different infeasible path detection algorithms, including the type and amount of flow information generated.

The rest of this paper is organized as follows: In Section 2, we discuss causes of infeasible paths and describe related work. In Section 3, we describe our research prototype, SWEET. Section 4 describes the different algorithms, and Section 5 presents an illustrating example. Section 6 presents analysis results, and in Section 7 we draw some conclusions and discuss future work.

This research has been supported by the KK-foundation through grant 2005/0271.

# 2 Causes of Infeasible Paths and Related Work

There are two different causes to infeasible paths. The first cause is semantic dependencies that always hold, as illustrated by the following code fragment:

if

$$(x < 0)$$

A else B; if  $(x > 2)$  then C else D

Here, both true-branches for the if statements are always in conflict<sup>1</sup>, and the corresponding path A-C can never be taken.

A second cause to infeasible paths is due to limitations of input data values. Such limitations can be used to further limit the set of feasible paths. For example, if we know that x>5 when the above code is executed, then we can conclude that the paths A-C, A-D, and B-D are all infeasible i.e., we find more infeasible paths with this additional knowledge.

Recent industrial WCET case-studies [7, 9, 17], have shown that it is important to develop good support for both loop bound analysis and infeasible path detection, thereby reducing the need for manual annotations. The case studies also showed that a mode- (giving a WCET estimate under certain system conditions) and input-sensitive WCET analysis often was preferable, in order to obtain better resource utilization and provide a better understanding of the system's timing characteristics. Thus, it should be important to develop input-sensitive infeasible path analyses.

There has been some work on automatic detection of infeasible paths for WCET analysis. Altenbernd [2] uses a combination of path enumeration, path pruning, and symbolic evaluation to find infeasible paths. Kountouris [13] studies detection of infeasible paths in the synchronous real-time language SIGNAL. Liu et al. [14] use symbolic evaluation of higher languages to avoid infeasible paths. Lundqvist and Stenström [15] find loop bounds and infeasible paths by symbolic simulation on the binary code. Healy et al. use value-dependent constraints to find infeasible paths [12]. Aljifri et al. [1] generate only the feasible paths using the concept of partially-known variables. Chen et al. [4] proposed a method that finds infeasible paths by identifying conflicts between assignments and branches, and between different branches.

The proposed infeasible path detection algorithms all use our flow analysis method abstract execution [10, 11], which is briefly described in the next section. This method has some similarities with the one of Lundqvist and Stenström [15], as well as with trace partitioning [3]. However, abstract execution uses a

more detailed value domain, and it is based on an abstract interpretation framework.

# 3 SWEET and Abstract Execution

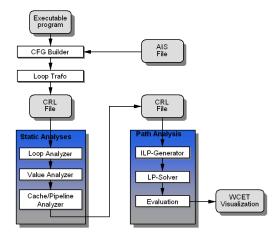

SWEET (SWEdish Execution time Tool) is a prototype WCET tool developed at Uppsala and Mälardalen University [16]. It consists of three main parts; a flow analysis which detects program flow constraints, a lowlevel analysis, where timing for program parts are obtained [6], and a final calculation where the longest execution path is extracted given information derived in the two preceding stages [8].

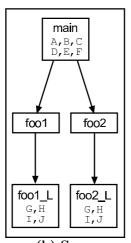

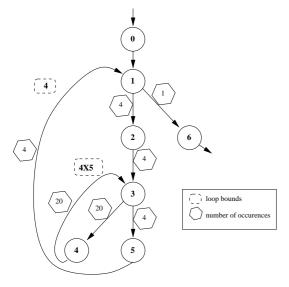

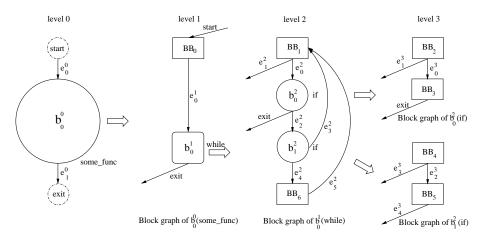

The current flow analysis of SWEET uses a *scope-graph* [8]. Each *scope* in the scope-graph is a different execution environment of a program, such as a function or a loop. See Figure 3 for an example. Our current scope-graph representation is context-sensitive, i.e., each call to a function or a loop in a function generates a different scope. Different calls to a function are analysed separately, which may yield higher precision but also a costlier analysis.

Abstract execution is a form of symbolic execution [10, 11], which is based on abstract interpretation. Rather than using traditional fixed-point iteration [5], abstract execution executes the program in the abstract domain, with abstract values for the program variables, and abstract versions of the operators in the language. For instance, the abstract domain can be the domain of intervals: each numeric variable will then hold an interval rather than a number, and each assignment will calculate a new interval from the current intervals held by the variables. As usual in abstract interpretation, the abstract value held by a variable, at some point, represents a set containing the actual concrete values that the variable can hold at that point.

With abstract values, conditionals cannot always be decided, and the abstract execution must then execute both branches. In order to curb the growing number of paths, *merging* of abstract values for different paths can take place. A merged abstract value then surely contains all the possible concrete values from both paths, and a single-path abstract execution, representing the execution of both paths, can continue from the merging point. Typical merge points are places where different program flows meet, like after if-statements or loops. Merging may yield abstract values that represent the possible set of concrete values in a less precise way: for instance, the merge of the intervals [6..6] and [10..11] is [6..11], which also contains the concrete values 7, 8, 9 not present in the original intervals.

SWEET currently supports abstract execution with intervals. It allows the user to control the placement of merge points, in order to explore different tradeoffs

$<sup>^{-1}</sup>$ We assume, for simplicity, that the value of x is not modified in A and B.

| i = INPUT; // i = [14] | iter | i at p        |                 |

|------------------------|------|---------------|-----------------|

| while (i < 10) {       | 1    | [14]          | min.            |

| // point p             | 2    | [36]          | <b>#iter:</b> 3 |

|                        | 3    | [58]          |                 |

| i=i+2;                 | 4    | [7 <b></b> 9] | max.            |

| }                      | 5    | [9 <b></b> 9] | <b>#iter:</b> 5 |

| // point q             | 6    | impossible    |                 |

(a) Example (b) Analysis (c) Result Figure 1. Example of abstract execution

between analysis speed and precision. Currently, the user can specify merge points to be one or more of the

following types: after if-statements, after loop bodies, after loop exits and after function exits.

Figure 1 gives a simple example of abstract execution with intervals. The loop in Figure 1(a) is abstractly executed in Figure 1(b). As iteration 4 and 5 are executed, the set of possible values of i is reduced until, finally, the set of values for the true branch of the loop condition is empty, the loop condition is evaluated to FALSE only, and the abstract execution of the loop terminates. During the abstract execution, we keep track of the iteration count of the loop body, and Figure 1(c) shows the resulting loop bounds.

The abstract interpretation framework guarantees that a calculated abstract value always represents the set of possible concrete values. Thus, no execution paths will be missed by the analysis. On the other hand, an abstract value may overestimate this set, which means that the analysis may yield program flow constraints that are not tight. This means that some infeasible paths might be reported as feasible. However, this is safe, since less information about infeasible paths only gives a possibly less tight WCET estimate.

We have created an abstract analysis domain for the data representation in C [11]. This allows us to handle C features like structs, arrays, pointers and type casts. We do not perform our analysis directly on the C source code. Instead, it is applied on an intermediate code format, making our flow analysis more generic and less dependent on C source characteristics.

The infeasible path analyses presented in this paper are implemented in SWEET as a part of the abstract execution. The abstract execution is input data sensitive, as illustrated in Figure 1, allowing the user to constrain the possible input data values. The result of the abstract execution is passed as flow information, flow facts [8], to the subsequent calculation phase. Flow facts are a kind of constraints on the execution count.

# 4 Algorithms for Infeasible Paths

We now present our three algorithms for infeasible path detection. Since they are based on abstract execution, which is input-sensitive, the analyses are inputsensitive as well.

All three algoritms have a similar overall structure. They augment each analysis state with a *recorder* keeping track of nodes and path(s) taken during a particular analysis of a scope. Each algorithm resets the recorder of a scope when starting a new iteration of the scope. They also associate a *collector* to each scope, which accumulates information about nodes and paths during iterations of the scope. In the end, each collector is used to generate flow facts for its scope.

# 4.1 Detecting Infeasible Nodes

The first algorithm finds infeasible nodes, that is: basic blocks which are never visited in any execution of a certain scope. Since there is one scope per context, the resulting flow information becomes context sensitive. An infeasible node is therefore not necessarily the same as dead code, since the basic block potentially can be executed in another context.

The recorder object is a bit array with one bit per node in the scope. These bits are all reset to zero at each iteration of the scope, and the bit of a node is set to one at each abstract execution of the node. Thus, a value of zero, after an iteration, means "definitely not executed in this iteration" and one means "may have been executed in this iteration".

The collector object is a similar bit array. Its bits are all initialized to zero, and the end of each iteration the new value of the collector object is set to the bitwise or of its old value and the current value of the recorder object. At termination, if the collector holds a zero for a node, then it is surely never executed in that scope, and a corresponding "infeasible node flow fact" can be generated. An example is:

scope : <> : #BB82 = 0;

specifying that basic block BB82 is not executed in any iteration of the scope  $\mathtt{scope}$ .

### 4.2 Detecting Infeasible Pair of Nodes

The second algorithm finds infeasible pairs of basic blocks, i.e., blocks which are always excluding each other during the same iteration of a scope. This gives additional knowledge as compared to the first analysis, since there might be nodes which both can be executed during some iteration of a scope, but which never can be executed together. The limitation is that infeasible paths with more than two selections can be missed.

The recorder object for this algorithm is a path (list of nodes) taken during an iteration. To limit the number of recorded nodes, only nodes after conditional branches are recorded. At the entry of a scope or at a new loop iteration, the path is emptied. Whenever a conditional branch is taken, we remember the branch by appending the corresponding node to end of the path. If both paths are taken, the analysis proceeds in two abstract states, one for each path.

The collector object is a triangular matrix which holds exclusion data. It is of size  $N \times N$ , where N is the number of possible branch outcomes (basic blocks) for the selections in the scope. The matrix can be triangular since the order of the elements in a pair is irrelevant. All elements in such a matrix are set to  $\bot$  in the beginning of the analysis, which means that no information is available to start with. A recorder list RL is added to the collector matrix M when an abstract state has reached the end of a loop body or a function scope. The collector is updated as follows:

```

for each node n_1 in RL do for each subsequent node n_2 to n_1 in RL do M[n_1,n_2]:=1 for each alternative branch node n_3 to n_2 do if M[n_1,n_3]=\bot then M[n_1,n_3]:=0 else M[n_1,n_3]:=M[n_1,n_3] OR 0

```

For example, if the path **A-C** was taken in the example in Section 2 we would have updated  $M[\mathbf{A}][\mathbf{C}]$  to 1 and  $M[\mathbf{A}][\mathbf{D}]$  with 0.

When the analysis has finished, the resulting collector matrix is investigated. Matrix positions with  $\bot$  mark pairs which have not been touched during the analysis. Some of them can never be executed together anyway due to the structure of the control graph, while the rest really are infeasible pairs. For the first type, generating flow facts will be superfluous. They could be identified using a reachability analysis. However, this is not included in the current implementation, so to avoid a large number of superfluous flow facts, no flow facts are currently generated for  $\bot$  positions.

If the matrix positions holds a 0, it marks a node pair that we surely know excludes each other for any iteration of the scope, so for this pair an "excluding pair flow fact" can be generated, like:

```

scope : <> : (#BB33 + #BB57) < 2;

specifying that for any iteration of scope the basic

blocks BB33 and BB57 are never executed together.</pre>

```

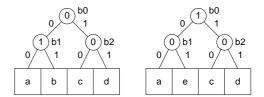

# **4.3** Detecting Infeasible Paths

The third algorithm finds sequences of nodes which are never executed together during the same iteration of a scope. The algorithm makes use of the fact that many infeasible paths can be efficiently represented by allowing them to share a common prefix (sub)path.

The recorder data object is now a tree where each tree node represents a path and has an associated

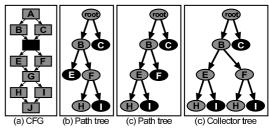

Figure 2. Example CFG and Path Trees

boolean specifying if the corresponding path is feasible or unfeasible. Similar to the recording in the second algorithm we only keep track of nodes taken after branches. However, the tree additionally keeps track of branch outcomes not taken.

Figure 2 gives an illustration of how the recorder tree works. Figure 2(a) gives a CFG with  $2^3 = 8$  structurally possible execution paths. Figure 2(b) gives the tree resulting from an execution taking the path **A-B-D-F-G-H-J** through the CFG. In the recorded tree the paths **A-C**, **A-B-D-E** and **A-B-D-F-G-I** have been marked as infeasible. Note that we, for the sake of efficiency, do not record any join nodes in the tree. Similarly, Figure 2(c) gives the tree resulting from an execution path of **A-B-D-E-G-H-J**. Note that the path **A-C** actually represents  $2^2 = 4$  number of paths through the CFG, since**A-C** is a prefix of all these paths.

For this algorithm the collector is the tree of paths obtained by merging all recorded trees for the scope. The basic idea of the collector is the same as in the first two algorithms, i.e., only keep infeasible path information which are true for all executions of the scope.

Figure 2(d) gives the collector tree resulting from merging the two trees in Figure 2(b) and Figure 2(c). Both trees has **A-C** as infeasible, and so does the collector tree. Since **A-B-D-E** is infeasible in Figure 2(b) but not in Figure 2(c), since it is part of the feasible **A-B-D-E-G-H-J** path, the collector tree cannot keep the path as infeasible. Instead, all paths (both infeasible and feasible) starting with the path **A-B-D-E** in Figure 2(c) are added to the collector tree. The infeasible path **A-B-D-F** in Figure 2(c) is extended similarly. The resulting collector tree in Figure 2(d) marks paths **A-C**, **A-B-D-F-G-I** and **A-B-D-E-G-I** as infeasible.

A collector tree CT is updated with a recorder tree RT as follows:

```

if RT is the first recorded tree reported CT := RT else for each infeasible path i in CT do if i is prefix to a feasible path in RT mark path i as feasible in CT add all paths with prefix i in RT to CT

```

(a) Example code

(b) Scopes

Figure 3. Code with several infeasible paths

After the analysis we create flow facts for the remaining infeasible paths in the collector tree. An example of such a flow fact is:

scope : <> : (#BB33 + #BB57 + #BB82) < 3; specifying that basic blocks BB33, BB57, and BB82 are never executed together for each iteration of scope.

# 5 Example

The example code in Figure 3(a) contains infeasible paths of several types (we assume that neither i, x or y are changed in the excluded code). It will be used to illustrate the algorithms we propose in the paper. The program contains five scopes; main, foo1, foo2 (the two calls to foo) and the corresponding loop scopes (foo1\_L and foo2\_L) in foo, as depicted in Figure 3(b). We can identify the following infeasible nodes, pairs and paths:

### 1. Infeasible nodes:

- E is an infeasible node in main, H and I are infeasible nodes in foo2\_L (limitations in input data).

### 2. Infeasible pairs:

- B-C, B-E, and D-E are infeasible pairs in main (contradicting conditions).

- A-E and C-E is an infeasible pair in main (limitations in input data).

- G-I and H-J are infeasible pairs in foo1\_L and foo2\_L (contradicting conditions).

- H-I is an infeasible pair in foo2\_L (limitations in input data).

### 3. Infeasible paths:

- A-D-E, B-C-E, B-C-F, and B-D-E are infeasible paths in main (contradicting conditions).

- B-D-E is an infeasible path in main (limitations in input data).

We note that infeasibility can be expressed in several ways, e.g., the infeasible pair **B-C** and the infeasible

paths **B-C-E** and **B-C-F** exclude the same paths.

# 6 Evaluation

| Program<br>adpcm | Adaptive pulse code modulation algo-                                                           | 879  |    |    |

|------------------|------------------------------------------------------------------------------------------------|------|----|----|

|                  | rithm.                                                                                         | 019  | 65 | 27 |

| bs               | Binary search for the array of 15 integer elements.                                            | 114  | 3  | 1  |

| bsort100         | Bubblesort program.                                                                            | 128  | 4  | 2  |

| cnt              | Counts non-negative numbers in a matrix.                                                       | 267  | 10 | 4  |

| compress         | Compression using lzw.                                                                         | 508  | 22 | 11 |

| cover            | Program for testing many paths.                                                                | 640  | 7  | 3  |

| crc              | Cyclic redundancy check computation on 40 bytes of data.                                       | 128  | 11 | 6  |

| duff             | Using "Duff's device" to copy 43 byte array.                                                   | 86   | 5  | 2  |

| edn              | Finite Impulse Response (FIR) filter calculations.                                             | 285  | 21 | 2  |

| expint           | Series expansion for computing an exponential integral function                                | 157  | 5  | 3  |

| fdct             | Fast Discrete Cosine Transform.                                                                | 239  | 4  | 2  |

| fft1             | 1024-point Fast Fourier Transform using the Cooly-Turkey algorithm.                            | 219  | 52 | 30 |

| fibcall          | Iterative Fibonacci, used to calculate fib(30).                                                | 72   | 3  | 1  |

| fir              | Finite impulse response filter (signal processing algorithms) over a 700 items long sample.    | 276  | 4  | 2  |

| insertsort       | Insertion sort on a reversed array of size 10.                                                 | 92   | 3  | 2  |

|                  |                                                                                                | 64   | 4  | 2  |

| jfdctint         | Discrete-cosine transformation on 8x8 pixel block.                                             | 375  | 5  | 2  |

| lcdnum           | Read ten values, output half to LCD.                                                           | 64   | 3  | 1  |

| ludcmp           | LU decomposition algorithm.                                                                    | 147  | 14 | 11 |

| matmult          | Matrix multiplication of two 20x20 matrices.                                                   | 163  | 12 | 7  |

| ndes             | Complex embedded code. A lot of bit<br>manipulation, shifts, array and matrix<br>calculations. | 231  | 25 | 12 |

| ns               | Search in a multi-dimensional array.                                                           | 535  | 6  | 4  |

| nsichneu         | Simulate an extended Petri net. Automatically generated code with more than 250 if-statements. | 4253 | 2  | 2  |

| qsort-exam       | Linear equations by LU decomposition.                                                          | 121  | 8  | 6  |

| qurt             | Root computation of quadratic equations.                                                       | 166  | 16 | 3  |

| select           | A function to select the Nth largest number in a floating point array.                         | 114  | 6  | 4  |

| statemate        | Automatically generated code.                                                                  | 1276 | 9  | 1  |

Table 1. Benchmark programs used

We have used programs from the Mälardalen WCET Benchmark to test our calculations. Table 1 gives some basic data about the programs (LC = lines of code), number of iteration scopes (#S), and number of (context-dependant) loops (#L). Table 2 shows the results of the different analyses. It shows the following information: Analysis time in seconds for abstract execution with loop bound analysis only (LB), number of found flow facts (#FF), and analysis time (Time) for each of the three algorithms (IN = infeasible nodes, EP = exclusive pairs, IP = infeasible paths). All measurements were performed on a 1.25 MHz PowerPC G4 processor, 1 Gb memory running Mac OS 10.4.6.

We see that we, with a small extra cost, can find infeasible nodes and paths for some of the benchmarks. It

| Program       | Time<br>LB | Alg.<br>#FF | 1 (IN)<br>Time | Alg. : | 2 (EP)<br>Time | Alg. 3 | 3 (IP)<br>Time |

|---------------|------------|-------------|----------------|--------|----------------|--------|----------------|

|               |            |             |                |        |                |        |                |

| adpcm         | 19.14      | 37          | 19.86          | 44     | 19.22          | 24     | 20.04          |

| bs            | 0.02       | 0           | 0.02           | 0      | 0.01           | 0      | 0.01           |

| bsort100      | 0.95       | 3           | 0.95           | 0      | 0.95           | 0      | 0.96           |

| cnt           | 0.21       | 1           | 0.22           | 0      | 0.21           | 0      | 0.23           |

| compress      | 0.58       | 63          | 0.61           | 9      | 0.59           | 6      | 0.58           |

| cover         | 0.71       | 114         | 1.65           | 1061   | 0.85           | 102    | 0.87           |

| crc           | 2.13       | 18          | 2.36           | 6      | 2.16           | 4      | 2.24           |

| duff          | 0.05       | 41          | 0.06           | 0      | 0.06           | 0      | 0.06           |

| edn           | 1.22       | 0           | 1.23           | 0      | 1.23           | 0      | 1.29           |

| expint        | 0.08       | 5           | 0.08           | 0      | 0.09           | 1      | 0.09           |

| fdct          | 0.01       | 14          | 0.01           | 0      | 0.01           | 0      | 0.01           |

| fft1          | 0.19       | 102         | 0.23           | 2      | 0.19           | 2      | 0.19           |

| fibcall       | 0.02       | 0           | 0.02           | 0      | 0.02           | 0      | 0.02           |

| fir           | 0.22       | 1           | 0.22           | 1      | 0.21           | 1      | 0.22           |

| insertsort    | 0.13       | 0           | 0.13           | 0      | 0.13           | 0      | 0.12           |

| janne_complex | 0.02       | 1           | 0.03           | 4      | 0.03           | 0      | 0.02           |

| jfdctint      | 0.03       | 0           | 0.03           | 0      | 0.03           | 0      | 0.03           |

| lcdnum        | 0.01       | 41          | 0.02           | 6      | 0.02           | 6      | 0.02           |

| ludcmp        | 1.88       | 3           | 1.88           | 1      | 1.89           | 1      | 1.88           |

| matmult       | 2.76       | 0           | 2.79           | 0      | 2.84           | 0      | 2.99           |

| ndes          | 8.02       | 11          | 9.39           | 3      | 8.10           | 1      | 8.13           |

| ns            | 1.00       | 1           | 1.01           | 0      | 1.01           | 0      | 1 <b>.</b> 05  |

| nsichneu      | 12.88      | 126         | 13.16          | 78150  | 1288.76        | 623    | 19.15          |

| qsort-exam    | 0.18       | 1           | 0.19           | 11     | 0.18           | 6      | 0.19           |

| qurt          | 0.08       | 27          | 0.11           | 7      | 0.08           | 5      | 0.08           |

| select        | 0.21       | 2           | 0.20           | 8      | 0.19           | 14     | 0.19           |

| statemate     | 0.14       | 256         | 0.15           | 5      | 0.13           | 32     | 0.13           |

Table 2. Analysis results

should be noted that these results are based on singlepath analysis, i.e., using a single input that leads to a single execution path. We expect more infeasible nodes and paths to be found when we analyse the programs with inputs that leads to multi-path analyses.

# 7 Conclusions and Future Work

We do think that our results are promising, but they are still somewhat preliminary: the benchmarks used so far are limited to single-path programs, and we only count the number of generated flow facts for infeasible paths. The next step is to extend the evaluation to a larger set of benchmarks, using multi-path analysis, and to also investigate the effect of the derived infeasible path information on the WCET estimate. In particular, we want to try out the algorithms on industrial real-time codes.

We also want to investigate tradeoffs between analysis time and WCET estimate precision. One possibility would be to generate flow information for individual iterations of a scope. This could give tighter WCET estimates, at the expense of longer analysis times. Another possibility is to generate non-context-sensitive flow facts, valid for all different call-sites of a particular function or loop. This will, in general, give less precise WCET estimates, but for a lower analysis cost.

### References

[1] H. Aljifri, A. Pons, and M. Tapia. Tighten the computation of worst-case execution-time by detecting feasible paths. In Proc. 19<sup>th</sup> IEEE International Performance, Computing, and

- Communications Conference (IPCCC2000). IEEE, February 2000.

- [2] P. Altenbernd. On the false path problem in hard real-time programs. In Proc. 8<sup>th</sup> Euromicro Workshop of Real-Time Systems, pages 102–107, June 1996.

- [3] Bruno Blanchet, Patrick Cousot, Radhia Cousot, Jérôme Feret, Laurent Mauborgne, Antoine Miné, David Monniaux, and Xavier Rival. Design and implementation of a special-purpose static program analyzer for safety-critical real-time embedded software. In The Essence of Computation; Complexity, Analysis, Transformation. Essays Dedicated to Neil D. Jones, volume 2566 of LNCS, pages 85–108. Springer-Verlag, 2002.

- [4] Ting Chen, Tulika Mitra, Abhik Roychoudhury, and Vivy Suhendra. Exploiting branch constraints without exhaustive path enumeration. In Reinhard Wilhelm, editor, Proc. 5<sup>th</sup> International Workshop on Worst-Case Execution Time Analysis, (WCET'2005), pages 40–43, Palma de Mallorca, July 2005.

- [5] Patrick Cousot and Radhia Cousot. Abstract interpretation: A unified lattice model for static analysis of programs by construction or approximation of fixpoints. In Proc. 4<sup>th</sup> ACM Symposium on Principles of Programming Languages, pages 238–252, Los Angeles, January 1977.

- [6] Jakob Engblom. Processor Pipelines and Static Worst-Case Execution Time Analysis. PhD thesis, Uppsala University, Dept. of Information Technology, Box 337, Uppsala, Sweden, April 2002. ISBN 91-554-5228-0.

- [7] O. Eriksson. Evaluation of Static Time Analysis for CC Systems. Master's thesis, Mälardalen University, August 2005.

- [8] Andreas Ermedahl. A Modular Tool Architecture for Worst-Case Execution Time Analysis. PhD thesis, Uppsala University, Dept. of Information Technology, Uppsala University, Sweden, June 2003.

- [9] Andreas Ermedahl, Jan Gustafsson, and Björn Lisper. Experiences from industrial WCET analysis case studies. In Proc. 5<sup>th</sup> International Workshop on Worst-Case Execution Time Analysis, (WCET'2005), pages 19–22, July 2005.

- [10] Jan Gustafsson. Analyzing Execution-Time of Object-Oriented Programs Using Abstract Interpretation. PhD thesis, Dept. of Information Technology, Uppsala University, Sweden, May 2000.

- [11] Jan Gustafsson, Andreas Ermedahl, and Björn Lisper. Towards a flow analysis for embedded system C programs. In Proc. 10<sup>th</sup> IEEE International Workshop on Object-oriented Real-time Dependable Systems (WORDS 2005), February 2005.

- [12] C. Healy and D. Whalley. Tighter Timing Predictions by Automatic Detection and Exploitation of Value-Dependent Constraints. In Proc. 5<sup>th</sup> IEEE Real-Time Technology and Applications Symposium (RTAS'99), June 1999.

- [13] Apostolos A. Kountouris. Safe and efficient elimination of infeasible execution paths in WCET estimation. In Proc. 3<sup>rd</sup> International Conference on Real-Time Computing Systems and Applications (RTCSA'96). IEEE, IEEE Computer Society Press, 1996.

- [14] Y. A. Liu and G. Gomez. Automatic accurate time-bound analysis for high-level languages. In Proc. ACM SIGPLAN Workshop on Languages, Compilers and Tools for Embedded Systems (LCTES'98), pages 31–40, June 1998.

- [15] Thomas Lundqvist. A WCET Analysis Method for Pipelined Microprocessors with Cache Memories. PhD thesis, Chalmers University of Technology, Göteborg, Sweden, June 2002.

- [16] Mälardalen University WCET project homepage, 2006. www.mrtc.mdh.se/projects/wcet.

- [17] Daniel Sehlberg. Static WCET analysis of task-oriented code for construction vehicles. Master's thesis, Mälardalen University, Västerås, Sweden, October 2005.

# Comparing WCET and Resource Demands of Trigonometric Functions Implemented as Iterative Calculations vs. Table-Lookup \*

Raimund Kirner, Markus Grössing, Peter Puschner Institut für Technische Informatik Technische Universität Wien, Austria raimund@ymars.tuwien.ac.at

#### Abstract

Trigonometric functions are often needed in embedded real-time software. To fulfill concrete resource demands, different implementation strategies of trigonometric functions are possible.

In this paper we analyze the resource demands of iterative calculations compared to other implementation strategies, using the trigonometric functions as a case study. By analyzing the worst-case execution time (WCET) of the different calculation techniques of trigonometric functions we got the surprising result that the WCET of iterative calculations is quite competitive to alternative calculation techniques, while their economics on memory demand is far superior. Finally, a discussion of the general applicability of the obtained results is given as a design guide for embedded software.

# 1 Introduction

For real-time systems in safety-critical environments it is indispensable to design the temporal behavior of the system based on knowledge of the worst-case execution time (WCET) of the real-time tasks. A general discussion on research directions in the area of WCET analysis can be found in [9].

Besides analyzing the timing behavior of programs we also look at software design techniques that proactively simplify the analysis of the WCET. We have described a general paradigm, which we call WCET-oriented programming [10]. The basic idea of WCET-oriented programming can be summarized as

the search for algorithms whose execution-time variability is small, for example, by avoiding input-data dependent control flow decisions whenever possible.

In this paper we study the characteristics of iteration-based computation techniques, we address interesting questions like whether these algorithms are suitable for real-time computing. For example, it is a common belief that iteration-based computation is critical, because a) long execution times due to high number of needed iterations and b) the problem of finding a precise upper iteration bound.

In the here-presented case study, we look at the behavior of trigonometric functions. The contribution of this paper is to connect the known properties of trigonometric functions to implementation techniques of real-time software and to provide an analysis of relevant characteristics like computation time and memory demands. Besides the interesting results obtained from our analysis, we also describe the application of WCET analysis to embedded software with floating point emulation.

### 2 Related Work

The work in this paper focuses on the properties of time-memory tradeoffs for real-time software. For example, one might design algorithms with shorter execution time by using more memory.

Sorting examples are sorting by counting, where a second array is used to sort elements with known relative positions based on their key in linear time, and Radix Sort [6]. Alternatively, lookup tables (LUT) can be used to reduce online calculations by deploying precalculated values. As an example for the use of lookup tables, see [7]. Time-space tradeoffs on dictionary attacks to break passwords are presented in [8]. Three further examples of applying time-memory tradeoffs are described in [11].

<sup>\*</sup>This work has been partially supported by the FIT-IT research project "Model-Based Development of distributed Embedded Control Systems (MoDECS)" and the ARTIST2 Network of Excellence of IST FP6.

# 3 Trigonometric Functions

For our study of different computation techniques we focus on trigonometric functions because they are heavily used in many scientific disciplines. Sine, cosine and tangent as well as their inverse functions play important roles not only in surveying, navigation, or scientific mathematics, but also in many other fields like acoustics, astronomy, computer graphics, electrical engineering and electronics, mechanical engineering, optics, etc.

First of all, it is important to keep in mind that the requirements on trigonometric functions are quite different depending on the application domain. For example, an application domain where performance is typically more important than precision is 3D computer graphics. The cosine is a fundamental operation in 3D rendering techniques like various shading methods, ray tracing, etc. [12]. Those rendering techniques have to use the trigonometric functions excessively often. Therefore, effective approximation techniques are very important to gain performance, while high precision is not a first-order requirement.

However, we are focusing more on the use of trigonometric functions in the domain of embedded real-time systems. They are used in mechanical applications, e.g., to determine distances in automation systems, or for controlling the movement of a robotic arm. Other important real-time applications are multimedia systems, where they are used to compute Fourier transforms (e.g., for audio processing) or discrete cosine transforms (for graphics) are performed. Further interesting application fields are applications that use ultrasound, optical devices, or statistical computations.

For the application of trigonometric functions in embedded real-time control systems, typically both, the numerical precision and the resource demands are relevant. For the following discussions of different calculation techniques we concentrate on the *cosine* function, since the other trigonometric functions are closely related respectively can be derived from it. We also discuss the maximum error for each calculation technique, which is needed for the comparison of iterative calculation and table-lookup in Section 4.

### 3.1 Iterative Approximation (Taylor Series)

In common implementations of trigonometric functions the Taylor series is used to approximate sine, cosine and tangent. There also exist other iterative algorithms like CORDIC [1], which are slower than Taylor series but easier to implement in hardware as it does not need multiplication operations. In this paper we

focus on the Taylor series because we are interested in implementations in software. Let us consider the power series implementation of cosine (Equation 1): to reach full double precision (as defined in [3]) a Taylor polynomial of degree 14 is needed. As only the coefficients of even powers are significant to calculate the cosine function, only seven coefficients are needed. We call this class of cosine implementation techniques CTAY-LOR.

$$\cos(x) = \sum_{n=0}^{\infty} (-1)^n \cdot \frac{x^{2n}}{(2n)!} \approx \sum_{n=0}^{7} (-1)^n \cdot \frac{x^{2n}}{(2n)!}$$

(1)

The constant coefficients do not need to be calculated at runtime everytime the function is called. Instead, they can be stored as static constants.

The accuracy of the power series decreases as the distance of the argument from the center grows. Therefore for trigonometric functions this distance is limited to  $\pi/4$ . As the center of sine, cosine, and tangent approximation is chosen to be zero the actual evaluation interval of these functions is  $[-\pi/4; \pi/4]$ . To evaluate arguments outside this interval an argument reduction needs to be performed [7].

To estimate the maximum error of a Taylor series implementation we need to consider the error at  $\pi/4$ , where the distance to the center of the power series is maximal.

The maximum error of Taylor series with n iterations is given by the remainder term  $R_{n+1}$  in Equation 2.

$$R_{n+1} = \frac{1}{n!} \int_0^x (x - t)^n \cdot \cos^{(n+1)}(t) dt =$$

$$= \cos(x) - \left(1 - \frac{x^2}{2!} + \frac{x^4}{4!} \cdot \dots + (-1)^n \cdot \frac{x^{2n}}{2n!}\right) \quad (2)$$

# 3.2 Approximation using Lookup Tables

Lookup tables are commonly used to replace runtime calculations with simpler lookup operations. Retrieving an array value from memory is usually much faster than making an expensive computation.

In the following we will take a look on three different implementations of lookup tables:

- Fast and simple lookup tables (FLUT)

- ullet Equidistantly interpolated lookup tables (*EDI-LUT*), and

- Lookup table with interpolation with smart placement of interpolation points (SMILUT)

### 3.2.1 Fast and Simple Table Lookup

The fast and simple lookup table (FLUT) is nothing more than a data array that stores pre-calculated function values of the function in it. The places where these values are taken are equidistant, so the array index fitting to a given argument can easily be computed. Each value in the array covers an interval of arguments. The biggest error occurs, where the function has its greatest gradient (see Equation 3. For example, a cosine lookup table in the interval  $[0; \pi/2]$  has its greatest gradient at  $\pi/2$ .

$$E_{max}(n) = \cos\left(\frac{\pi}{2} - \frac{\pi}{4(n-1)}\right) = \sin\left(\frac{\pi}{4(n-1)}\right) (3)$$

The advantage of FLUT is that it is easy to implement and the estimation of the timing behavior is simple. The performance according to speed is very good but accuracy requirements should not be too high. To enhance accuracy or to reduce the table size if a particular level of accuracy is given other methods like EDILUT and SMILUT can be used.

# 3.2.2 Table Lookup with Equidistant Interpolation

An equidistant interpolated lookup table (EDILUT) reaches significantly higher accuracy compared to a FLUT of the same size. The price to pay is a little more arithmetics and so longer execution time.

The entries of an EDILUT are the function values of equidistantly distributed places of the input interval. In the case of a cosine EDILUT the input interval is  $[0;\pi/2]$ . In a cosine calculation, first the two interpolation points next to the given argument are determined. Then a straight line through these two points is calculated and the argument is set into this straight interpolation line. With this method accuracy can be increased significantly.

The maximum error of EDILUT occurs not on the place with the greatest gradient, like it was the case for FLUT, but on the place with the greatest curvature. For our cosine function this is the case near the origin, so we expect the greatest error to occur in the first interpolation interval. The error of the interpolation in the first interval can be calculated by subtracting the linear interpolation between the first two interpolation points from the function. By deriving this function and setting to zero, the exact place of the maximum error is retrieved. Applying this value to the error function gives the maximum absolute error (Equation 4) for a concrete lookup table size n of EDILUT.

$$E_{max}(n) = \cos\left(\sin^{-1}(k)\right) - k \cdot \sin^{-1}(k) - 1,$$

$$k = -\frac{1 - \cos\frac{\pi}{2(n-1)}}{\frac{\pi}{2(n-1)}}$$

(4)

# 3.2.3 Table Lookup with Smart Interpolation

A smart interpolated lookup table (SMILUT) is a further improvement of EDILUT. In a SMILUT the interpolation points are not equidistantly distributed in the input interval but in a smarter way. The function for mapping the input interval into the range of array indices should be rather simple. We map the input interval to the indices using the squareroot function. The result is an improvement of accuracy.

With this placement we achieve that the maximum error does not occur within the first interpolation interval but rather in the middle of the overall input interval.

As the squareroot function might be too expensive to compute, we considered an alternative implementation for finding the correct interpolation interval, namely using binary search.

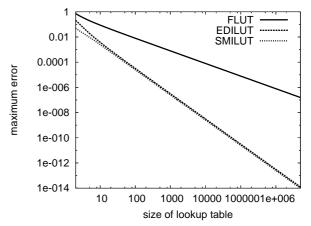

Figure 1. Maximum Absolute Error of FLUT, EDI-LUT, and SMILUT

To complete the discussion about LUT-based solutions, a comparison of the accuracy in dependence of the size of the lookup array is given in Figure 1<sup>-1</sup>.

<sup>&</sup>lt;sup>1</sup>Note that due to range limitations in the numerical calculation, the size values above 2000 are extrapolated values to show the tendency of the graph.

# 4 Comparison of Iterative vs. LUTbased Techniques

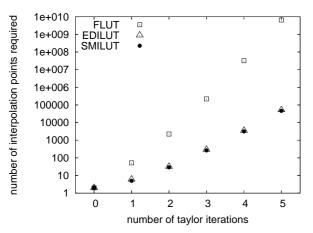

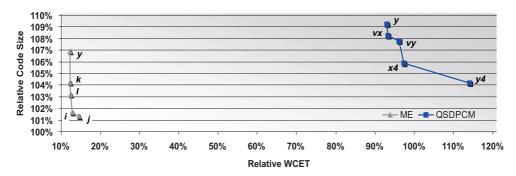

A comparison of different iteration numbers of Taylor series implementations to the three lookup table approaches is depicted in Figure 2. It is shown how many entries a particular type of lookup table needs to exceed the accuracy of different Taylor series implementations.

As the maximum error of FLUT and EDILUT can be calculated analytically, these two variants can be easily compared to the Taylor series. For the comparison of SMILUT a simple tool was developed to experimentally determine the required size of the SMILUT to reach the accuracy of the different Taylor series implementations. This tool determines the maximum error of a SMILUT for a given array size. If the error is too big the array size is increased. The program terminates when the accuracy of the SMILUT exceeds a given limit, e.g., the accuracy of a particular Taylor implementation.

As shown in Figure 2 the accuracy of FLUT is much worse than the accuracy of the other LUT implementations. SMILUT performs slightly better than EDILUT. One can see that the size of lookup tables of any type grows exponentially with the number of Taylor iterations. Thus, if high accuracy requirements need to be met, the use of lookup tables may not be feasible or sensible to approximate trigonometric functions - the memory consumption of these algorithms is too high.

Figure 2. Necessary LUT Size to Match the Accuracy of Taylor Series

# 5 Experimental Evaluation

In Section 3 we described the theoretical properties of different calculation techniques of trigonometric

functions. Lets now look at the different calculation techniques from a practical point of view. Especially interesting for the use of trigonometric functions in embedded real-time systems are their resource demands. Therefore, we analyzed their memory footprints in data and code memory, and calculated an upper bound of their worst-case execution time (WCET).

# 5.1 Studied Algorithms

To analyze the properties of the different computation techniques discussed in Section 3 on a concrete computer platform, we implemented several variants of the cosine function. We implemented the cosine function for the *double* data type of ANSI C (which is typically the 64-bit IEEE floating point format [3]).

Two iterative cosine variants belonging to CTAY-LOR were implemented, one which is a straight forward implementation of the Taylor-formula and one with precalculation of the coefficients of the Taylor-terms.

On the other side the three LUT-based variants of Section 3.2 have been implemented: FLUT the straight forward method, EDILUT which uses linear interpolation and SMILUT, an implementation using binary search to find the correct interpolation point within the LUT. Compared to EDILUT it is highly performance oriented and uses more precomputed results, requiring three LUTs.

Some characteristic parameters of the different cosine implementations are given in Table 1. The column #BB denotes the number of basic blocks of the generated object code. The DataMem columns give the required number of bytes to store the intermediate data and the LUT. It is given first in parametric form as a function of the LUT size N, and second for the concrete case N=1000. The column CodeMem denotes the net code size, i.e., without counting the standard library functions which are linked by the compiler. The byte values are given for the Infineon C167 processor, a 16bit architecture.

### 5.2 WCET Analysis

In the following we describe how we derived the WCET of the different cosine implementation techniques. Our WCET analysis tool  $calc\_wcet\_167$   $^2$  uses static timing analysis to calculate an upper bound of a task's WCET. The target architecture for the tool is the processor C167 from Infineon, for which the GCC compiler was ported by the company  $HighTec\ EDV$

<sup>&</sup>lt;sup>2</sup>http://www.wcet.at/tools.html

|                  |     | DataM                 | lem       |         |

|------------------|-----|-----------------------|-----------|---------|

| $Function\ name$ | #BB | (parametric)          | (N=1000)  | CodeMem |

|                  |     | [bytes]               | [bytes]   | [bytes] |

| CTAYLOR          | 22  | 28                    | n.a.      | 720     |

| $CTAYLOR\_tab$   | 19  | 90                    | n.a.      | 598     |

| FLUT             | 13  | 10+N·8                | 8 010     | 456     |

| EDILUT           | 15  | 34 + N.8              | 8 034     | 902     |

| SMILUT           | 23  | $30 + (N+1) \cdot 24$ | $24\ 054$ | 536     |

**Table 1. Implemented Calculation Variants of the Cosine Function**

Systeme GmbH<sup>3</sup>. The integration of optimizing compilation into the WCET analysis is described in [5]. The development and verification of the timing model for the Infineon C167 is documented in [2]. Because the Infineon C167 processor has a relatively simple architecture, the overestimation of the calculated WCET bound of our tool is tight, maximal 5%, but typically less than 2%, provided the control flow is precisely modelled by flow constraints [2].

The cosine implementations were written in WCETC, based on a subset of ANSI C but providing additional features to annotate the source code with flow information to guide the WCET analysis tool [4].

The WCET analysis of the cosine implementations itself did not require anything special to mention. However, the overall WCET analysis was not easy because the Infineon C167 processor does not have a floating point engine in hardware. For such architectures the compiler links extra program code that emulates the floating point computations in software (libsgnu.a provided by HighTec). To perform the WCET analysis we disassembled the object code of the library and annotated it at assembly code level with flow information.

The final WCET analysis results of the different cosine implementations are given in Table 2. Besides the properties of the concrete implementations, these values are generally rather high because we assumed a slow hardware configuration with slow external memory. The first of the WCET columns shows the WCET in a parametric form. This is only relevant for the iterative implementations, where *iter* is the number of loop iterations used to iteratively refine the result based on the Taylor series of the cosine function. The other four WCET columns show the WCET bound of the iterative algorithms for different iteration counts.

# 5.3 Discussion

The results of the general analysis of the maximum absolute error for CTAYLOR and of the maximum

absolute error of FLUT, EDILUT, and SMILUT together with the precision relationsship between CTAY-LOR and LUT-based methods (Figure 2) can be combined with the results from the concrete implementation to reason about the pros and cons of the different computation paradigms.

To demonstrate how this can be done, lets assume that for a concrete project one needs a cosine function providing a maximal error of less than  $2.5 \cdot 10^{-8}$ . Evaluating Equation 2 at  $\pi/4$  it follows that one would need 4 iterations ( $\equiv 5$  Taylor terms) with the CTAYLOR methods. To replace the CTAYLOR method later by an adequate LUT-based method one could deduce from Figure 2 the required LUT size to match at least the same precision. For example, to obtain the same quality with EDILUT or SMILUT, one has to choose an LUT size of N > 3000!

From Table 1 we can see that in this case the additional memory demand for the LUT-based methods is significant. The FLUT method, though it is relatively fast, is completely out of choice as it would require an LUT size of  $N>10^5$ . If performance really is the most important issue, then according to Table 2 one has to use the SMILUT implementation. But surprisingly, the CTAYLOR methods are not that bad regarding the WCET compared to SMILUT. As a rough indicator using our example, one would need only 90 bytes data memory when using CTAYLOR\_tab compared to the more than 72kB when using SMILUT. The code size is almost the same between these two implementations.

Another benefit of the CTAYLOR methods is their anytime characteristic. In case a CTAYLOR method gets interrupted, there is still some accuracy of the result available, for example, to move a robot arm at least in the intended direction, hoping that the control will be refined in the next round by a more accurate result. Depending on the application, this can be an advantage of iteration-based CTAYLOR methods compared to the LUT-based methods.

<sup>3</sup>http://www.hightec-rt.com

|                  |                                       | WCET     | [cycles] |             |          |

|------------------|---------------------------------------|----------|----------|-------------|----------|

| $Function\ name$ | (parametric)                          | (iter=1) | (iter=3) | (iter=4)    | (iter=7) |

| CTAYLOR          | $23\ 140 + \text{iter} \cdot 79\ 500$ | 102 640  | 261 640  | 341 140     | 579 640  |

| $CTAYLOR\_tab$   | $23\ 380 + \text{iter} \cdot 49\ 200$ | 72580    | 170 980  | $220 \ 180$ | 367 780  |

| FLUT             | 136 840                               | n.a.     | n.a.     | n.a.        | n.a.     |

| EDILUT           | 276 640                               | n.a.     | n.a.     | n.a.        | n.a.     |

| SMILUT           | 120 540                               | n.a.     | n.a.     | n.a.        | n.a.     |

Table 2. Calculated WCET of the Cosine Functions (Target Processor: Infineon C167)

### Generality of the Results

In our concrete case study of the cosine function it has been shown that the WCET of the iterative calculation is quite competitive to table-lookup while the economics on memory demand is far superior.

Iterative calculations generally provide the same advantages as long as they have a relatively compact calculation step within each iteration and the termination speed of the iterative calculation is reasonable.

As a further example, the *Newton method* to solve equations numerically tends to provide such a behavior, provided that the start value is already within the local convergence interval of the solution. There are many instantiations of the Newton method in practice, e.g., the *Heron method* to calculate the square root of a number.

# 6 Summary and Conclusion

Motivated by our general effort to study the suitability of different algorithms for real-time computing, we looked at different calculation techniques of trigonometric functions, because of their use in a wide range of technical applications.

One of the central conclusions is that whenever memory is highly constrained, iteration-based methods are very useful, because they tend to demand much less memory while still providing reasonable accuracy of results. And quite important, the performance overhead of iteration-based methods is not that high, even in our case study where we calculated the WCET for the C167, a processor that emulates floating point arithmetics in software. Further, the WCET analysis itself was an interesting experience, as we had to analyze routines of the floating-point emulation library by disassembling the object code.

In general, in embedded real-time systems, where size of memory is typically restricted, iterative algorithms can be a memory-efficient calculation technique without significant performance costs compared to LUT-based methods, as long as a reasonable termination speed of the iterative calculation is ensured.

# References

- [1] R. Andraka. A survey of cordic algorithms for fpga based computers. In *Proc. ACM/SIGDA 6th International Symposium on Field Programmable Gate Arrays*, pages 191–200, 1998.

- [2] P. Atanassov. Experimental Assessment of Worst-Case Program Execution Times. PhD thesis, Technische Universität Wien, Vienna, May 2003.

- [3] IEEE. IEEE Standard 754-1985 for Binary Floating-Point Arithmetic. IEEE, New York, 1987. Reprinted in SIGPLAN Notices 22,2,9-25.

- [4] R. Kirner. The programming language WCETC. Technical report, Technische Universität Wien, Institut für Technische Informatik, Treitlstr. 1-3/182-1, 1040 Vienna, Austria, 2002.

- [5] R. Kirner. Extending Optimising Compilation to Support Worst-Case Execution Time Analysis. PhD thesis, Technische Universität Wien, Vienna, Austria, May 2003.

- [6] D. E. Knuth. The Art of Computer Programming -Sorting and Searching, volume 3. Addison Wesly, New York, USA, 2nd edition, 1998. ISBN 0-201-89685-0.

- [7] J. N. Lygouras. Memory reduction in look-up tables for fast symmetric function generators. *IEEE Transactions on Instrumentation and Measurement*, 48(6):1254–1258, Dec. 1999.

- [8] A. Narayanan and V. Shmatikov. Fast dictionary attacks on passwords using time-space tradeoff. In Proc. 12th ACM conference on Computer and Communications Security, pages 364–372, New York, NY, USA, 2005. ACM Press.

- [9] P. Puschner and A. Burns. A review of worst-case execution-time analysis. *Journal of Real-Time Sys*tems, 18(2/3):115–128, May 2000.

- [10] P. Puschner and R. Kirner. Avoiding timing problems in real-time software. In Proc. IEEE Computer Society's Workshop on Software Technologies for Future Embedded Systems, May 2003.

- [11] M. Stamp. Once upon a time-memory tradeoff. Technical report, San José State University, San José, California, USA, July 2003.

- [12] A. Watt. 3D Computer Graphics. Addison Wesley, 3rd edition, Dec. 1999. ISBN: 0201398559.

# **History-based Schemes and Implicit Path Enumeration**

Claire Burguière and Christine Rochange

Institut de Recherche en Informatique de Toulouse

Université Paul Sabatier

31062 Toulouse cedex 9, France

{burguier,rochange}@irit.fr

### **Abstract**

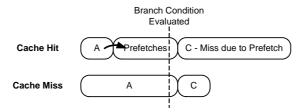

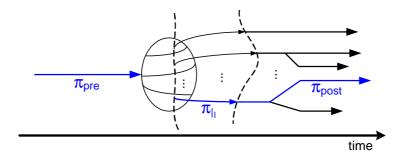

The Implicit Path Enumeration Technique is often used to compute the WCET of control-intensive programs. This method does not consider execution paths as ordered sequences of basic blocks but instead as sets of basic blocks with their respective execution counts. This way of describing an execution path is adequate to compute its execution time, provided that safe individual WCETs for the blocks are known. Implicit path enumeration has also been used to analyze hardware schemes like instructions caches or branch predictors the behavior of which depends on the execution history. However, implicit paths do not completely capture the execution history since they do not express the order in which the basic blocks are executed. Then the estimated longest path might not be feasible and the estimated WCET might be overly pessimistic. This problem has been raised for cache analysis. In this paper, we show that it arises more acutely for branch prediction and we propose a solution to tighten the estimation of the misprediction counts.

### 1 Introduction

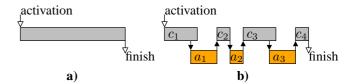

The difficulty of evaluating the Worst-Case Execution Time of a real-time application comes from the – generally – huge number of possible paths that makes it intractable to analyze each of them individually. The single-path programming paradigm [9] would noticeably simplify the WCET computation but it has a cost in terms of performance that might not be acceptable. This is the reason why much research effort has been put on developing WCET evaluation approaches based on static analysis [10]. These approaches factorize the efforts by building up the WCET of the complete program from the individual WCETs of basic blocks. The Implicit Path Enumeration Technique [13], also known as *IPET*, is a very popular method for WCET calculation. It expresses the search of the WCET as an Integer Linear Programming problem where the program execution

time is to be maximized under some constraints on the execution counts of the basic blocks. With this technique, an execution path is defined by the set of the executed blocks with their respective execution counts but the order in which they are executed is not expressed.

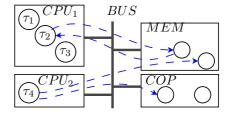

More and more complex processors are used in real-time embedded systems and it is a real challenge to take into account all of their advanced features in WCET analysis. In particular, some mechanisms have a behaviour that depends on the execution history which is difficult to capture by static analysis. These mechanisms include cache memories and dynamic branch predictors. In this paper, we consider bimodal branch prediction as an example of such schemes.

Various methods to take branch prediction into account have been proposed in the litterature. As explained below, we focus on the approach by Li *et al.* [12] that we have later extended [5] to take into account 2-bit prediction counters. In this paper, we show that both models can lead to overestimated WCET because the worst-case number of mispredictions computed by IPET would correspond to an infeasible execution path. We show how they should be revised to only reflect feasible behaviours of the branch prediction scheme. Experimental results show that the revised model tighten the estimated WCET.

The paper is organized as follows. In Section 2, we illustrate the differences between implicit and explicit execution paths by an example. Section 3 gives an overview of dynamic branch prediction and lists previous work on branch prediction modeling for WCET analysis. We show how misprediction counts can be over-estimated in Section 4 and we propose an extended model to tighten the estimated WCET in Section 5. Section 6 concludes the paper.

# 2 Implicit vs. explicit execution paths

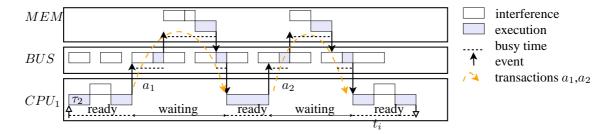

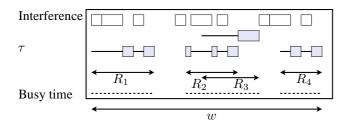

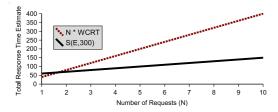

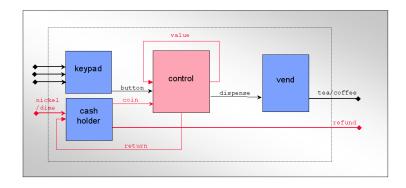

Figure 1 gives an example code that will be used throughout this paper and Figure 2 shows the corresponding CFG.

```

#define M 4

#define N 6

int main() {

int i, j;

int mat[M][N];

for (i=0; i<M; i++) {

mat[i][0]=1;

for (j=0; j<N; j++)

mat[i][j]=i+j;

}

}</pre>

```

Figure 1. Example code.

Figure 2. Example CFG.

**Explicit paths.** An *explicit* execution path is an ordered list of the executed basic blocks. In our example, the only possible execution path is defined by the sequence of blocks:

$$\Big( b1 - b2 - (b3 - b4)_{\times 5} - b3 - b5 \Big)_{\times 4} - b1 - b6$$

Path-based WCET analysis [11][16] explores explicit paths but this might be costly because, as said before, a program may have many possible (explicit) paths. Some static WCET analysis methods simplify the path exploration while still considering explicit paths. For example, the Extended Timing Schema [17][15] works on the Syntax Tree.

**Implicit paths.** The IPET method [13] considers *implicit* paths. An implicit path is defined by the list of its basic blocks and of their execution counts. The implicit path corresponding to the explicit path given above is:

$$(b1\times5, b2\times4, b3\times24, b4\times20, b5\times4, b6\times1)$$

An implicit path defines many possible explicit paths but, in general, most of them are infeasible. For example, the implicit path given above could be expanded as below, where the inner loop is executed three times with a single iteration and once with 17 iterations, which is not consistent with the program semantics.

$$\begin{array}{l} (b1 - b2 - b3 - b4 - b3 - b5)_{\times 3} - b1 - b2 - \\ - (b3 - b4)_{\times 17} - b3 - b5 - b1 - b6 \end{array}$$

In the IPET method, the execution time of an implicit path is computed by adding the individual execution times of the basic blocks weighted by their execution counts. The WCET is obtained by maximizing the total execution time under some contraints that link the execution counts of the nodes and edges of the CFG: structural constraints directly express the CFG structure and flow constraints express loop bounds and infeasible paths.

As long as implicit paths are only used to compute a global execution time by summing individual times, there is no need to provide further information about the program semantics. However, when some mechanisms based on the execution history have to be modeled within the same framework, the *implicit* expression of execution paths might not be sufficient. This problem has been raised in the case of instruction cache analysis [14]. In this paper, our purpose is to show that it can also arise when modeling branch prediction and that it is a bit more complex in this case. However, we will provide a solution to get round it.

# 3 Branch prediction and WCET estimation

### 3.1 Bimodal branch prediction

Branch prediction enhances the pipeline performance by allowing the speculative fetching of instructions along the predicted path after a conditional branch has been encountered and until it is resolved. If the branch was mispredicted, the pipeline is flushed and the other path is fetched and executed. In the hardware *bimodal* branch predictor [18], the branch direction is predicted from a 2-bit saturating counter stored in the *Branch History Table* (which is indexed by the branch PC). If the branch is predicted as taken (counter equal to 11 or 10), the target address is read in the *Branch Target Buffer*, otherwise the instruction fetch proceeds sequentially. When the branch is later computed, the prediction counter is updated as shown in Figure 3.

# 3.2 Modeling branch prediction for WCET estimation

### 3.2.1 Background

Modeling bimodal dynamic branch predictors for WCET analysis has been the purpose of several papers these last

Figure 3. Bimodal branch prediction.

years. Some of the proposed techniques are *decoupled* from the pipeline analysis. Colin and Puaut [8] use static simulation to determine whether the prediction counter associated to a branch might be corrupted by another branch. Then they combine these results with an analysis of the behaviour of the 2-bit counters related to algorithmic structures to calculate bounds on the misprediction counts. Other works assume that branch aliasing can be prevented and refine the analysis of branching patterns related to algorithmic structures [1][6]. Once misprediction counts have been determined, the estimated execution time is augmented by the corresponding misprediction penalties.

To take into account tigher *per-branch* misprediction penalties, branch prediction modeling can also be *integrated* to the WCET computation with IPET [2][4]. Li *et al.* go further by completely modeling the behaviour of the branch prediction scheme within the IPET model [12]. They take conflicts in the Branch History Table into account but they only consider 1-bit prediction counters. In [5] we argue for techniques to prevent aliasing and we extend their model by considering 2-bit counters. Our discussion here is based on this last work.

Modeling branch prediction as part of WCET computation has several advantages: (1) any kind of loop can be analyzed, even if it is not well structured (*e.g.* several exit points); (2) the analysis of branches implementing conditional structures does not require any particular effort; (3) per-branch misprediction penalties can be specified.

### 3.2.2 Baseline model

The estimation of misprediction counts is combined to WCET computation by IPET by the way of additional constraints that: (a) express the way the prediction counters evolve; and (b) link the evolution of the prediction counters to the execution counts of the blocks and edges in the CFG. In this section, we give a simplified overview of the model. The variables used to evaluate the WCET by IPET are:

| $x_i$                           | execution count of block i                                                     |

|---------------------------------|--------------------------------------------------------------------------------|

| $x_{i\stackrel{d}{ ightarrow}}$ | execution count of the edge leaving block $i$ when the branch direction is $d$ |

|                                 | $x_i = x_{i,0} + x_{i,1}$                                                      |

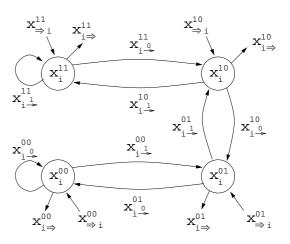

The constraints added to model a bimodal branch predictor (without aliasing in the Branch History Table) use some additional variables (execution counts) presented in Figure 4.

Figure 4. Variables used to model branch prediction for block *i*

The set of possible states for a 2-bit branch prediction counter is denoted as  $\mathcal{C} = \{00, 01, 10, 11\}$  and the set of possible directions d after a branch is denoted as  $\mathcal{D} = \{0, 1\}$ . The constraints that model the way the prediction for the branch of block i evolves are:

$$\begin{cases}

x_i^{00} = x_{i \to i}^{00} + x_{i \to i}^{01} + x_{\Rightarrow i}^{00} \\

x_i^{01} = x_{i \to i}^{10} + x_{i \to i}^{00} + x_{\Rightarrow i}^{01} \\

x_i^{10} = x_{i \to i}^{10} + x_{i \to i}^{01} + x_{\Rightarrow i}^{10} \\

x_i^{10} = x_{i \to i}^{11} + x_{i \to i}^{10} + x_{\Rightarrow i}^{11} \\

x_i^{11} = x_{i \to i}^{11} + x_{i \to i}^{10} + x_{\Rightarrow i}^{11}

\end{cases}$$

(1)

$$\forall c \in \mathcal{C}, x_i^c = x_{i,0}^c + x_{i,1}^c + x_{i \Rightarrow}^c \tag{2}$$

The variables related to branch prediction are linked to the execution counts of basic blocks and edges by the following constraints:

$$x_i = \sum_{c} x_i^c \quad \forall d \in \mathcal{D}, x_{i \xrightarrow{d}} = \sum_{c} x_{i \xrightarrow{d}}^c + \sum_{c} x_{i \xrightarrow{d}}^c$$

(3)

For the initial and final state of the branch counter of block i, we can write:

$$\sum_{c} x_{\Rightarrow i}^{c} = 1 \qquad \sum_{c} x_{i \Rightarrow}^{c} = 1 \qquad (4)$$

Finally, mispredictions counts are derived from:

$$m_i = x_{i\stackrel{1}{\longrightarrow}}^{00} + x_{i\stackrel{1}{\longrightarrow}}^{01} + x_{i\stackrel{1}{\longrightarrow}}^{10} + x_{i\stackrel{1}{\longrightarrow}}^{11}$$

(5)

# 4 Branch prediction modeling and implicit path enumeration

# 4.1 Example code

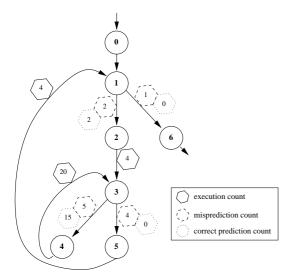

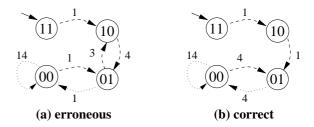

We have analyzed the branch predictor behavior for our example code using the model described in the previous section. Figure 5 shows the results we obtained. The branch at the end of block 3 controls the inner loop that iterates 5 times (then the branch is executed 6 times for each execution of the loop: it is *not taken* 5 times and *taken* once). The inner loop is repeated 4 times: block 3 is then executed 24 times on the global execution path (20 times as *not taken* and 4 times as *taken*). The numbers given in the dotted and dashed hexagons stand for the correct and erroneous branch prediction counts.

Figure 5. Results for the example code