## 7th International Workshop on Worst-Case Execution Time Analysis

WCET 2007, July 3, 2007, Pisa, Italy

Edited by Christine Rochange

#### Editor

Christine Rochange TRACE Group IRIT, Université Paul Sabatier 118 Route de Narbonne 31062 Toulouse Cedex 9, France rochange@irit.fr

ACM Classification 1998

C.4 Performance of Systems, D.2.4 Software/Program Verification

#### ISBN 978-3-939897-05-7

Published online and open access by

Schloss Dagstuhl – Leibniz-Center for Informatics GmbH, Dagstuhl Publishing, Saarbrücken/Wadern, Germany.

Publication date

November, 2007.

Bibliographic information published by the Deutsche Nationalbibliothek

The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available in the Internet at http://dnb.d-nb.de.

#### License

This work is licensed under a Creative Commons Attribution-Noncommercial-No Derivative Works license: http://creativecommons.org/licenses/by-nc-nd/3.0/legalcode.

In brief, this license authorizes each and everybody to share (to copy, distribute and transmit) the work under the following conditions, without impairing or restricting the author's moral rights:

- Attribution: The work must be attributed to its authors.

- Noncommercial: The work may not be used for commercial purposes.

- No derivation: It is not allowed to alter or transform this work.

The copyright is retained by the corresponding authors.

Digital Object Identifier: 10.4230/OASIcs.WCET.2007.i

#### OASIcs - OpenAccess Series in Informatics

OASIcs aims at a suitable publication venue to publish peer-reviewed collections of papers emerging from a scientific event. OASIcs volumes are published according to the principle of Open Access, i.e., they are available online and free of charge.

ISSN 2190-6807

www.dagstuhl.de/oasics

## 2007 WCET Abstracts Collection 7th Intl. Workshop on Worst-Case Execution Time (WCET) Analysis

Christine Rochange

Université Paul Sabatier, F rochange@irit.fr

Abstract. The workshop on Worst-Case Execution Time Analysis is a satellite event to the annual Euromicro Conference on Real-Time Systems. It brings together people that are interested in all aspects of timing analysis for real-time systems. In the 2007 edition, 13 papers were presented, organized into four sessions: methods for WCET computation, low-level analysis, system-level analysis and flow-analysis. The workshop was also the opportunity to report from the 2006 WCET tool challenge.

**Keywords.** Worst-case execution time, real-time systems, timing analysis

## 2007 WCET Preface – Proceedings of the 7th Intl. Workshop on Worst-Case Execution Time Analysis (WCET'07)

Jan Gustafsson

The purpose of the WCET Tool Challenge is to be able to study, compare and discuss the properties of different WCET tools and approaches, to define common metrics, and to enhance the existing benchmarks. The WCET Tool Challenge has been designed to find a good balance between openness for a wide range of analysis approaches, and specific participation guidelines to provide a level playing field. This should make results transparent and facilitate friendly competition among the participants. This short report presents conclusions from from the WCET Tool Challenge 2006 as well as some ideas for the WCET Tool Challenge 2006.

Keywords: WCET'07, workshop proceedings, abstracts collection Full Paper: http://drops.dagstuhl.de/opus/volltexte/2007/1198

#### Automatic Amortised Worst-Case Execution Time Analysis

Christoph A. Herrmann; Armelle Bonenfant; Kevin Hammond; Steffen Jost; Hans-Wolfgang Loidl; Robert Pointon

Our research focuses on formally bounded WCET analysis, where we aim to provide absolute guarantees on execution time bounds. In this paper, we describe how amortisation can be used to improve the quality of the results that are obtained from a fully-automatic and formally guaranteed WCET analysis, by delivering analysis results that are parameterised on specific input patterns and which take account of relations between these patterns. We have implemented our approach to give a tool that is capable of predicting execution costs for a typical embedded system development platform, a Renesas board with a Renesas M32C/85U processor. We show that not only is the amortised approach applicable in theory, but that it can be applied automatically to yield good WCET results.

Keywords: Amortisation, functional programming, performance measurement, static analysis, type and effect systems, worst-case execution time

Full Paper: http://drops.dagstuhl.de/opus/volltexte/2007/1187

#### Clustering Worst-Case Execution Times for Software Components

Johan Fredriksson; Thomas Nolte; Andreas Ermedahl; Mikael Nolin

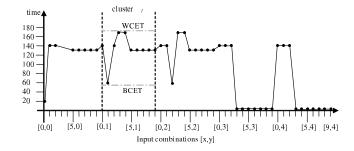

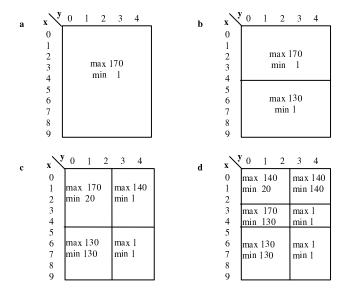

For component-based systems, classical techniques for Worst-Case Execution Time (WCET) estimation produce unacceptable overestimations of a componentsWCET. This is because software components more general behavior, required in order to facilitate reuse. Existing tools and methods in the context of Component-Based Software Engineering (CBSE) do not yet adequately consider reusable analyses. We present a method that allows different WCETs to be associated with subsets of a components behavior by clustering WCETs with respect to behavior. The method is intended to be used for enabling reusable WCET analysis for reusable software components. We illustrate our technique and demonstrate its potential in achieving tight WCET-estimates for components with rich behavior.

Keywords: Worst-case execution time, Software components, Reuse, Analysis

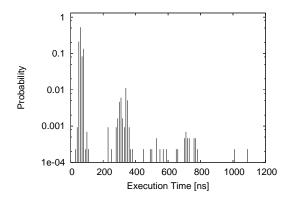

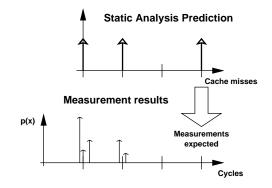

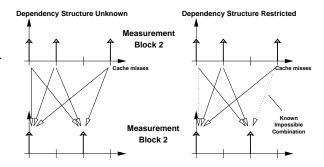

#### Measurements or Static Analysis or Both?

Stefan M. Petters; Patryk Zadarnowski; Gernot Heiser

To date, measurement-based WCET analysis and static analysis have largely been seen as being at odds with each other. We argue that instead they should be considered complementary, and that the combination of both represents a promising approach that provides benefits over either individual approach. In this paper we discuss in some detail how we aim to improve on our probabilistic measurement-based technique by adding static cache analysis. Specifically we are planning to make use of recent advances within the functional languages research community. The objective of this paper is not to present finished or almost finished work. Instead we hope to trigger discussion and solicit feedback from the community in order to avoid pitfalls experienced by others and to help focus our research.

Keywords: Measurement based Approach, Static Analysis, Cache Analysis, Proof, Overestimation

Full Paper: http://drops.dagstuhl.de/opus/volltexte/2007/1188

#### A Framework for Static Analysis of VHDL Code

Marc Schlickling; Markus Pister

Software in real time systems underlies strict timing constraints. These are among others hard deadlines regarding the worst-case execution time (WCET) of the application. Thus, the computation of a safe and precise WCET is a key issuel for validating the behavior of safety-critical systems, e.g. the flight control system in avionics or the airbag control software in the automotive industry. Saarland University and AbsInt Angewandte Informatik GmbH have developed a successful approach for computing the WCET of a task. The resulting tool, called aiT, is based on the abstract interpretation [3, 4] of timing models of the processor and its periphery. Such timing models are hand-crafted and therefore error-prone. Additionally the modeling requires a hard engineering effort, so that the development process is very time consuming. Because modern processors are synthesized from a formal hardware specification, e.g., in VHDL or VERILOG, the hand-crafted timing model can be developed by manually analyzing the processor specification. Due to the complexity of this step, there is a need for support tools that ease the creation of analyzes on such specifications. This paper introduces the primer work on a framework for static analyzes on VHDL.

Keywords: Timing Analysis, Worst-Case Execution Time, VHDL, Static Analysis

#### 4

#### Towards Symbolic State Traversal for Efficient WCET Analysis of Abstract Pipeline and Cache Models

Stephan Wilhelm; Björn Wachter

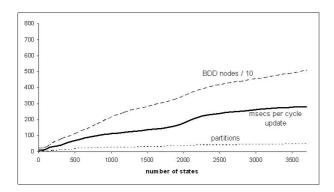

Static program analysis is a proven approach for obtaining safe and tight upper bounds on the worst-case execution time (WCET) of program tasks. It requires an analysis on the microarchitectural level, most notably pipeline and cache analysis. In our approach, the integrated pipeline and cache analysis operates on sets of possible abstract hardware states. Due to the growth of CPU complexity and the existence of timing anomalies, the analysis must handle an increasing number of possible abstract states for each program point. Symbolic methods have been proposed as a way to reduce memory consumption and improve runtime in order to keep pace with the growing hardware complexity. This paper presents the advances made since the original proposal and discusses a compact representation of abstract caches for integration with symbolic pipeline analysis.

WCET, worst-case execution time, hard real-time, embedded systems, abstract interpretation, pipeline analysis, cache analysis, symbolic state traversal BDD

Full Paper: http://drops.dagstuhl.de/opus/volltexte/2007/1190

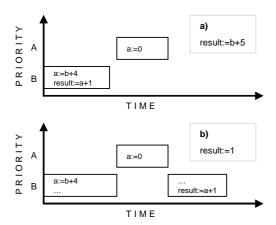

#### Finding DU-Paths for Testing of Multi-Tasking Real-Time Systems using WCET Analysis

Daniel Sundmark; Anders Petterson; Christer Sandberg; Andreas Ermedahl; Henrik Thane

Memory corruption is one of the most common software failures. For sequential software and multi- tasking software with synchronized data accesses, it has been shown that program faults causing memory cor- ruption can be detected by analyzing the relations be-tween defines and uses of variables (DU-based testing). However, such methods are insufficient in preemptive systems, since they lack the ability to detect inter-task shared variable dependencies. In this paper, we propose the use of a system level shared variable DU analy- sis of preemptive multi-tasking real-time software. By deriving temporal attributes of each access to shared data using WCET analysis, and combining this information with the real-time schedule information, our method also detects intertask shared variable dependencies. The paper also describes how we extended the SWEET tool to derive these temporal attributes.

Keuwords: Testing, Real-time systems, WCET analysis, data flow

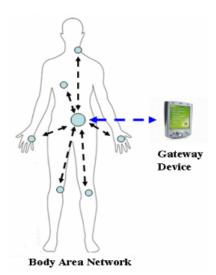

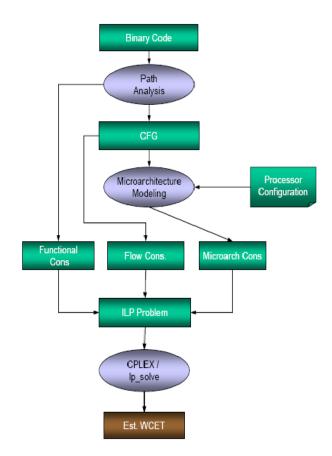

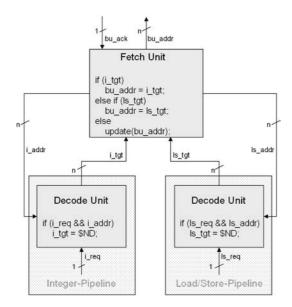

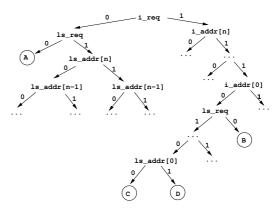

#### Timing Analysis of Body Area Network Applications

Liang Yun; Abhik Roychoudhury; Tulika Mitra

Body area network (BAN) applications have stringent timing requirements. The timing behavior of a BAN application is determined not only by the software complexity, inputs, and architecture, but also by the timing behavior of the peripherals. This paper presents systematic timing analysis of such applications, deployed for health-care monitoring of patients staying at home. This monitoring is used to achieve prompt notification of the hospital when a patient shows abnormal vital signs. Due to the safetycritical nature of these applications, worst-case execution time (WCET) analysis is extremely important.

Keywords: WCET analysis of Peripherals, Body Area Network applications

Full Paper: http://drops.dagstuhl.de/opus/volltexte/2007/1192

#### Data-Flow Based Detection of Loop Bounds

Christoph Cullmann; Florian Martin

To calculate the WCET of a program, safe upper bounds on the number of loop iterations for all loops in the program are needed. As the manual annotation of all loops with such bounds is difficult and time consuming, the WCET analyzer aiT originally developed by Saarland University and AbsInt GmbH uses static analysis to determine the needed bounds as far as possible. This paper describes a novel data-flow based analysis for aiT to calculate the needed loop bounds on the assembler level. The new method is compared with a pattern based loop analysis already in use by this tool.

Keywords: WCET analysis, loop bound detection, flow analysisFull Paper: http://drops.dagstuhl.de/opus/volltexte/2007/1193

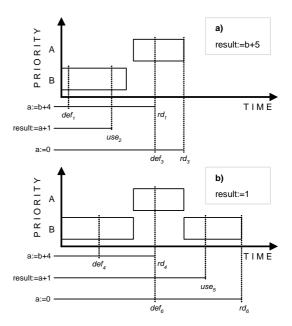

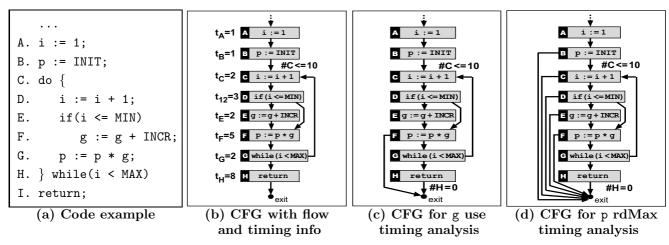

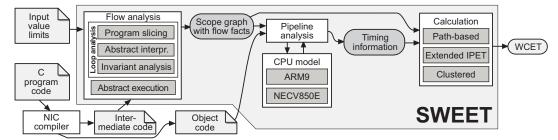

#### Loop Bound Analysis based on a Combination of Program Slicing, Abstract Interpretation, and Invariant Analysis

Andreas, Ermedahl; Christer Sandberg; Jan Gustafsson; Stefan Bygde; Björn Lisper

Static Worst-Case Execution Time (WCET) analysis is a technique to derive upper bounds for the execution times of programs. Such bounds are crucial when designing and verifying real-time systems. A key component for static derivation of precise WCET estimates is upper bounds on the number of times different loops can be iterated. In this paper we present an approach for deriving upper loop bounds based on a combination of standard program analysis techniques.

#### 6 Ch. Rochange

The idea is to bound the number of different states in the loop which can influence the exit conditions. Given that the loop terminates, this number provides an upper loop bound. An algorithm based on the approach has been implemented in our WCET analysis tool SWEET. We evaluate the algorithm on a number of standard WCET benchmarks, giving evidence that it is capable to derive valid bounds for many types of loops.

Keywords: WCET analysis, loop-bound analysis, program slicing, abstract interpretation, invariant analysis

Full Paper: http://drops.dagstuhl.de/opus/volltexte/2007/1194

#### Analysing Switch-Case Tables by Partial Evaluation

Niklas Holsti

This paper describes ongoing work aimed at the construction of formal cost models and analyses to yield verifiable guarantees of resource usage in the context of real-time embedded systems. Our work is conducted in terms of the domain-specific language Hume, a language that combines functional programming for computations with finitestate automata for specifying reactive systems. We outline an approach in which high-level information derived from source-code analysis can be combined with worst-case execution time information obtained from high quality abstract interpretation of low-level binary code.

Keywords: WCET, switch-case, partial evaluation

Full Paper: http://drops.dagstuhl.de/opus/volltexte/2007/1195

#### Analysis of path exclusion at the machine code level

Ingmar Stein; Florian Martin

We present a method to find static path exclusions in a control flow graph in order to refine the WCET analysis. Using this information, some infeasible paths can be discarded during the ILP-based longest path analysis which helps to improve precision. The new analysis works at the assembly level and uses the Omega library to evaluate Presburger formulas.

Keywords: Flow-constraint, control flow graph, path exclusion

#### WCET Analysis: The Annotation Language Challenge

Raimund Kirner; Jens Knoop; Adrian Prantl; Markus Schordan; Ingomar Wenzel

Worst-case execution time (WCET) analysis is indispensable for the successful design and development of systems, which, in addition to their functional constraints, have to satisfy hard real-time constraints. The expressiveness and usability of annotation languages, which are used by algorithms and tools for WCET analysis in order to separate feasible from infeasible program paths, have a crucial impact on the precision and performance of these algorithms and tools. In this paper, we thus propose to complement the WCET tool challenge, which has recently successfully been launched, by a second closely related challenge: the WCET annotation language challenge. We believe that contributions towards mastering this challenge will be essential for the next major step of advancing the field of WCET analysis.

Keywords: Worst-case execution time analysis, WCET, path description, annotation language challenge, expressiveness, convenience

#### Report from the WCET Tool Challenge 2006 Ideas for the WCET Tool Challenge 2008

Jan Gustafsson

Department of Computer Science and Electronics, Mälardalen University

jan.gustafsson@mdh.se

#### Abstract

The purpose of the WCET Tool Challenge is to be able to study, compare and discuss the properties of different WCET tools and approaches, to define common metrics, and to enhance the existing benchmarks. The WCET Tool Challenge has been designed to find a good balance between openness for a wide range of analysis approaches, and specific participation guidelines to provide a level playing field. This should make results transparent and facilitate friendly competition among the participants.

This short report presents conclusions from from the WCET Tool Challenge 2006 as well as some ideas for the WCET Tool Challenge 2006.

#### 1 Goals

The goals of the WCET Tool Challenge are the following:

- To exhibit the wide range of timing analysis tools available today

- using static program analysis, or

- combining analysis and measurements,

- for various target processors,

- in various application domains,

- supporting various programming languages and design tools,

- academic, commercial; free or at a charge.

- To illuminate the features, abilities and intended uses of each tool

- in finding the feasible execution paths in the SW,

- in modelling complex processor and system HW,

- in deriving useful WCET bounds or estimates,

- in usability, scalability and adaptability,

- in the range of supported targets (processors, compilers, ..)

- To collect and maintain a growing set of community standard benchmark programs and related test suites that

- contain typical (both easy and hard) programming constructs,

- can be analyzed by several tools with comparable results,

- test enough of the actual behaviour of each benchmark to satisfy measurement-based tools and to validate results from static-analysis tools, and ideally, have known exact answers (paths and WCETs).

For more details, consult the Challenge web page http://www.idt.mdh.se/personal/jgn/challenge/.

#### 2 WCET Tool Challenge 2006

The first WCET Tool Challenge was performed during the autumn of 2006. It concentrated on three aspects of WCET analysis:

- 1. flow analysis,

- 2. required user interaction,

- 3. performance.

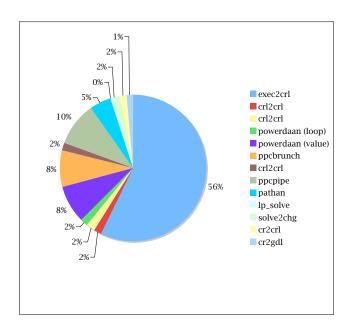

Two companies (developing the commercial tools aiT and Bound-T) and three research groups (developing the research tools SWEET, Chronos and MTime) participated. The actual work with the tools was made by an external user and the development teams. The evaluation was targeted on a set of benchmark programs.

The report was presented at ISoLA 2006 as two separate papers. The first [1] was the main report; the other [3] presented the experiences from the external user. There is also a technical report available [2], which contains more details.

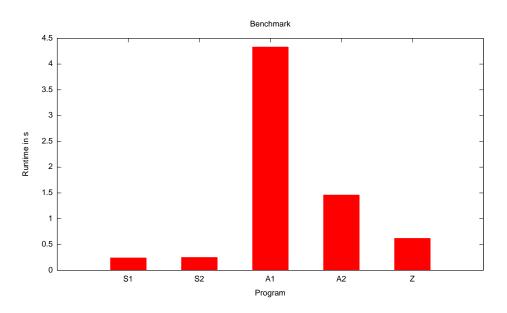

#### 2.1 Results from WCET Tool Challenge 2006

This first Challenge was performed successfully in spite of some initial unclearness, debate and delay. We noted that there is no common format of the results from the different tests, and that different developers have made different tests sometimes. We draw the following conclusions:

- The tests have been a real challenge to the participating WCET tools. We have a success range from 0% to 100% in terms of how many of the benchmark programs that were analyzable by a certain tool.

- The tests have clearly pointed out problems existing in the tools as well as in the benchmarks and the used compilers.

- Most of the tools find more than half of the loop bounds automatically. Only one tool finds infeasible paths automatically.

- Several bugs in both the tools and the benchmarks have been corrected during the Challenge.

- Actual WCET estimates cannot be compared this time since the developers support different processors and compilers.

- The quality of WCET estimates is hard to judge for all tools but aiT, since aiT was the only tool to provide measurements for some of the benchmarks. Chronos provided simulated values that indicate the possible size of overestimation.

#### 3 WCET Tool Challenge 2008

Since the work to perform the Challenge is extensive, both for the work group and the developers, we decided to make the event bi-annual. Another reason was to have some tool development time between tests, so real progress could be observed from one Challenge to the next. This means that the next Challenge is to be performed 2008.

A number of actions have to be made to enhance the next Challenge compared to the first. Some of them are:

- Update benchmarks and the setup of the Challenge according to the feedback from the WCET Tool Challenge 2006.

- Extend the active working group to 2 or 3 persons.

- Create a reference group which will act as a support to the working group.

- Try to extend the number of participants. Tools like OTAWA and Heptane, and measurement-based tools (e.g., Rapita, SYMTA/P) should be invited again. There are also some new tools entering the

- WCET analysis scene (like TimeBounder from Korea).

- The procedure of identifying test data (inputs) necessary for measurement-based based tools should be defined.

- The inputs for the worst-case behavior of the benchmark programs should be defined.

- Be more detailed concerning tests and format of result reports.

- Exclude benchmark programs that are redundant in terms of what is tested.

- Include industrial code, e.g. aero space and automotive code (e.g., Daimler-Chrysler code).

- If possible, include more automatically generated code.

- Try to focus on one common processor (ARM7?) to be able to compare WCET estimates.

- Define hardware setup in detail so comparative lowlevel analysis (e.g., cache and branch prediction analysis) can be performed.

#### References

- [1] J. Gustafsson. The worst case execution time tool challenge 2006. In *Proc.* 2<sup>nd</sup> International Symposium on Leveraging Applications of Formal Methods (ISOLA'06), Nov. 2006.

- [2] J. Gustafsson. WCET challenge 2006 technical report. MRTC report 1209, 2007. Technical Report MRTC report 1209, 2007, Mälardalen University Real-Time Research Centre, Mälardalen University University, Västerås, Sweden, 2007.

- [3] L. Tan. The worst case execution time tool challenge 2006: The external test. In Proc. 2<sup>nd</sup> International Symposium on Leveraging Applications of Formal Methods (ISOLA'06), Nov. 2006.

#### A Framework for Static Analysis of VHDL Code

#### Marc Schlickling Saarland University & AbsInt GmbH schlickling@cs.uni-sb.de

## Markus Pister Saarland University & AbsInt GmbH pister@cs.uni-sb.de

#### **Abstract**

Software in real time systems underlies strict timing constraints. These are among others hard deadlines regarding the worst-case execution time (WCET) of the application. Thus, the computation of a safe and precise WCET is a key issue<sup>1</sup> for validating the behavior of safety-critical systems, e.g. the flight control system in avionics or the airbag control software in the automotive industry.

Saarland University and AbsInt Angewandte Informatik GmbH have developed a successful approach for computing the WCET of a task. The resulting tool, called aiT, is based on the abstract interpretation [3, 4] of timing models of the processor and its periphery. Such timing models are hand-crafted and therefore error-prone. Additionally the modeling requires a hard engineering effort, so that the development process is very time consuming.

Because modern processors are synthesized from a formal hardware specification, e.g., in VHDL or VERILOG, the hand-crafted timing model can be developed by manually analyzing the processor specification.

Due to the complexity of this step, there is a need for support tools that ease the creation of analyzes on such specifications. This paper introduces the primer work on a framework for static analyzes on VHDL.

#### 1 Introduction

During the last years, embedded systems have become nearly omnipresent in everyday life. Embedded processors are used in a variety of application fields: health-care technology, multimedia applications, telecommunication, automotive and avionics, weapon guidance, etc. Common characteristics of many applications are that high computation performance has to be obtained at low cost and low power consumption. Moreover many applications have safety-critical characteristics and must satisfy hard real-time constraints. This leads to an additional requirement to be respected in embedded system design: the requirement of predictable performance. It is not enough for microprocessors to yield high peak performance, but it should also

be possible to statically guarantee their worst-case performance. Contemporary superscalar architectures are characterized by deep complex pipelines, often with features like out-of-order execution, branch prediction, and speculative execution which make determining the guaranteed performance of applications a difficult task [8].

The worst-case execution time analyzer *aiT* originally developed by *Saarland University* and *AbsInt Angewandte Informatik GmbH* is a tool for computing safe and precise upper bounds of the worst-case execution time (WCET) of tasks. The computation is based on the *abstract interpretation* [3, 4] of *timing models* of the processor core and its system controller [18, 19]. The tool takes the executable as input and performs several static analyzes on it. The input is transformed into an intermediate representation called *Control-Flow Representation Language* (CRL)<sup>2</sup> [13], on which the analyzes are based. Further details about the *aiT* tool-chain can be found in [6].

The computation of the WCET of a task mainly depends on the so called *pipeline analysis* in which the behavior of the processor pipeline and the underlying system controller are modeled. This is done by abstracting from everything that is not needed for the timing behavior of the processor pipeline. Further details about how to create a pipeline analysis can be found in [18].

As of today, these models are hand-crafted and only obtainable with a hard engineering effort. Therefore, the development of a pipeline analysis is a very time consuming and error prone process. And the complexity dramatically increases along with each new processor generation used within embedded systems<sup>3</sup>.

A formal processor specification (usually coded in a *Hardware description language* like VHDL or VERILOG) can be very helpful in the creation of a pipeline analysis. But even then, one needs to manually analyze the specification in order to find suitable abstractions. In order to ease this we introduce a framework for static analyzes of VHDL de-

<sup>&</sup>lt;sup>1</sup>besides the functional correctness of the system

<sup>&</sup>lt;sup>2</sup>In our framework we use the second version of this intermediate representation called CRL2

<sup>&</sup>lt;sup>3</sup>As of today, these embedded processors are rather similar to and featureful as modern desktop processors.

scriptions. To this end, we developed a VHDL frontend that transforms the specification into the intermediate language CRL2 mentioned above. Different static analyzers can be generated using the *Program Analyzer Generator* PAG based on a formal analysis specification.

The paper is structured as follows: Section 2 contains a description of PAG and CRL2. Section 3 then details the semantics of VHDL. In Section 4, our analysis framework is described and illustrated with an example in Section 5. Section 6 shows some experimental results. Section 7 gives an outlook on future work and Section 8 concludes.

#### 2 Preliminaries

We use PAG to generate static program analyzers based on a control flow graph. The next two sections introduce the basics of the control flow representation language and the Program Analyzer Generator.

#### 2.1 CRL

The Control-Flow Representation Language (CRL2) was developed to provide an intermediate format that simplifies analyzes and optimizations on a control flow graph [13].

A control flow graph is a representation, using graph notation, of all paths that might be traversed through a program during its execution. Nodes in the graph represent basic blocks, i.e. straight-line pieces of code. Directed edges are used to represent jumps in the control flow.

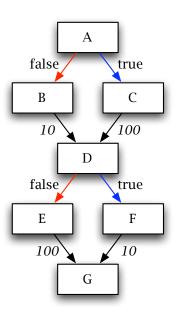

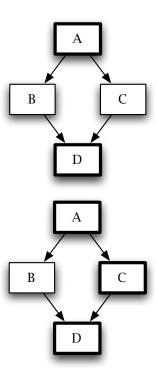

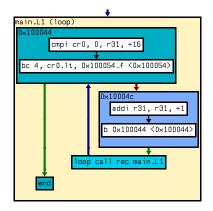

Assuming that the control flow graph is always well-formed, the structure of CRL2 is hierarchically organized in instructions, basic blocks and routines. Thereby, the former is always completely enclosed within the latter. A sample control flow graph is given in Figure 1 showing two routines (simul and environment). The edge between the two routines indicates a call dependency, each routine call is represented through *call/return blocks* in the callee's routine. The call/return blocks ease interprocedural control flow analyzes [17] and are more or less placeholders for the branch to the called routine.

CRL2 is a very flexible language by virtue of an attributevalue concept, i.e. each element can be extended by attributes coding arbitrary information. To process a program represented by its control flow graph, PAG can be used.

#### 2.2 Program Analyzer Generator

PAG is a powerful tool for generating program analyzers. Based on a high-level specification of a data flow problem, PAG automatically generates a program analyzer<sup>4</sup> which can be used in arbitrary applications [14].

The triple (K, L, []] is called a *data flow problem* for a complete lattice<sup>5</sup> L and a control flow graph K, if  $[]]: N \to$

Figure 1: Sample CRL2-graph

$(L \to L)$  is a function assigning functions from  $L \to L$  to the nodes of K. These functions are called *transition functions* and are used for updating the data flow value during analysis.

More details on data flow problems can be found in [16], a description of the specification language for PAG in [1].

#### 3 VHDL Semantics

VHDL is an IEEE Standard defined in IEEE 1076 [2, 12]. The focus of the language ranges from specifying circuits at wavefront level to describing large system behaviors with high-level constructs. As a result, the standard is huge. The focus of this paper only considers the *synthesizable subset* of VHDL, defined in [11].

A VHDL description of a circuit consists of an interface declaration defining the in- and output signals of the circuit and of one or more implementation(s). In VHDL, the first is called an *entity*, the second an *architecture*. Figure 2 shows a simple 3-bit counter.

The implementation is given in form of two *processes* (P1 and P2). Each process executes its code, whenever one of the *signals* contained in the processes *sensitivity lists* (*clk* and *rst* for P1, *cnt* for P2) changes its value. After execution of all statements, execution suspends until another

<sup>&</sup>lt;sup>4</sup>in ANSI-C

<sup>&</sup>lt;sup>5</sup>A *complete lattice* is a partially ordered set in which all subsets have both a supremum and an infimum. An example for a complete lattice is the

power set of a given set, ordered by inclusion. The supremum is given by the union and the infimum by the intersection of subsets.

```

entity comb_logic is

port(a,b,c:in std_logic;res:out std_logic);

end;

architecture rtl of comb_logic is

signal wire: std_logic;

component and_gate is

port(u,v:in std_logic;w:out std_logic);

end component;

component or_gate is

port(x,y:in std_logic;z:out std_logic);

end component;

begin

and_gate port map(a,b,wire);

or_gate port map(wire,c,res);

end;

```

Figure 3: Composition of VHDL components

```

entity counter is

port(clk:in std_logic; rst:in std_logic;

val: out std_logic_vector(2 downto 0));

end:

architecture rtl of counter is

signal cnt:std_logic_vector(2 downto 0);

begin

process(clk, rst) is

P1:

<u>if</u> (rst='1') <u>then</u>

cnt <= "000";

elsif (rising_edge(clk)) then

cnt \le cnt + \dot{1};

end if;

end;

P2: process(cnt) is

val \le cnt;

end;

end;

```

Figure 2: 3-bit counter in VHDL

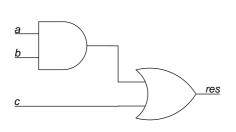

change of at least one signals value. Thus, the sensitivity list of a process is an implicit wait-statement at its end.  $^6$  VHDL also supports component-based circuit specifications. Figure 3 gives an example for hierarchical circuit composition. Here, the combinatorial function  $res = a \land b \lor c$  is modeled using a logical-and and a logical-or gate. Having a hierarchical composed specification of a circuit, *elaboration* has to be performed in order to get a flat definition of it. Elaboration does all the required renaming for unifying names, wires all structural descriptions, etc. The result is one large entity consisting of a number of processes and some locally defined signals.

A VHDL process consists of a set of local *variables* that are only accessible from inside the process. By contrast, local signals can be accessed by more than one process, but only

one process is allowed to drive the value of a signal. Within a process, execution of statements is done sequentially.

VHDL makes a distinction between the assignments to a variable and to a signal. Assigning a value to a variable takes effect immediately (i.e., the next reference of this variable returns the newly assigned value), whereas the assignment of a value to a signal is only *scheduled* to be the future value (i.e., the next reference returns the old value). E.g., in Figure 2, the signal assignment cnt<=cnt+'1'; schedules the next value of cnt to be cnt plus one, but the next reference val<=cnt; schedules the next value of val to be the *current* value of cnt. These future values take effect as soon as all processes *suspend* their execution. The semantics of a VHDL program, i.e. a set of processes, can be described as follows:

- 1. Execute processes until they suspend.

- 2. If all processes are suspended, make all scheduled signal assignments visible at once.

- 3. If there is a process being sensitive on a signal having changed its value, resume this process and go to step 1.

- 4. Otherwise, an external signal must change its value (e.g., the clock signal). If this happens, resume all processes waiting for this signal and go to step 1.

Thus, the semantics of VHDL can be seen as a two-level semantics: sequential process execution at its first, signal update and process revocation at its second level.

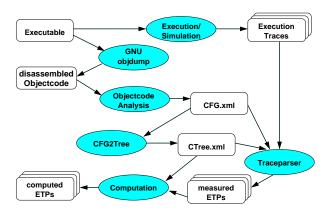

#### 4 A VHDL analysis framework

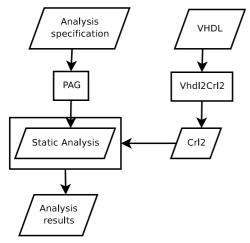

As mentioned in the introduction, we present here a framework for statically analyzing VHDL code using abstract interpretation. The structure and data flow of our framework is illustrated in Figure 4. As input, we have the VHDL model that we want to analyze and a PAG specification for a static analysis. We developed a tool

<sup>&</sup>lt;sup>6</sup>In VHDL, the use of explicit wait-statements and sensitivity lists is exclusive. We assume, that the only place within a process, where wait-statements may occur, is at the end of the body of a process.

<sup>&</sup>lt;sup>7</sup>In full VHDL, *resolution functions* can be used for value computation of signals being driven by two or more processes.

Figure 4: Structure of VHDL analysis framework

| VHDL element                  | CRL2 element  |

|-------------------------------|---------------|

| Process,                      | Routine       |

| Function,                     |               |

| Procedure,                    |               |

| Concurrent signal assignment, |               |

| Concurrent procedure call,    |               |

| Loop                          |               |

| Function calls                | Routine calls |

| Procedure calls               | Routine calls |

| Sequential statement          | Instruction   |

Table 1: Mapping VHDL to CRL2

called Vhdl2Crl2 that transforms the VHDL into semantically equivalent CRL2 constructs. From the analysis specification, PAG generates a static analyzer that works on the CRL2 description. And at the end, the analysis emits its results. The mentioned components in our framework are now detailed in the following subsections.

#### 4.1 Mapping VHDL to CRL2

In order to express a VHDL description in semantically equivalent CRL2 constructs, we need to give a mapping from VHDL components to CRL2 components. Table 1 shows this mapping. Processes are transformed into routines as well as functions, procedures, concurrent signal assignments, concurrent procedure calls and loops. The transformation of loops to routines roughly means, that the whole loop body is moved into a newly created routine and the original location of the loop is replaced by a call to the new loop routine. This improves the quality of static analyzes of loops. More details on this so called *Loop transformation* can be found in [15].

The correspondence of function/procedure calls to routine calls as well as the mapping of sequential statements to instructions is rather intuitive.

#### 4.2 VHDL as a sequential program

Regarding the special semantics of VHDL (cf. Section 3), we need to express the input VHDL description as a sequential program whose control flow is represented by CRL2. The reason for this is that we want to generate the analyzer itself from a concise PAG specification, where PAG is an analyzer generator for programs (cf. Section 2). As mentioned in Section 3, variables in VHDL are process-local and processes run in parallel. Additionally signal assignments only take effect after all processes have finished their execution. These semantics directly induce that there are no side effects between the different VHDL processes. So, we can serialize their execution without changing the semantics of the whole model.

In order to formulate a VHDL description as a sequential program, we just need to choose an arbitrary execution order among the processes and iteratively execute them in this order. The program then consists of a routine, let's call it simul (cf. Figure 1), whose body contains routine calls, where each called routine represents one of the former VHDL processes. Additionally each such routine call for an original process it guarded with a conditional statement that evaluates the sensitivity list of the process. If at least one of the signals in the sensitivity list has changed, the call is taken. The result of such a transformation from a VHDL model into a sequential program is shown in Figure 1. Here, you can see the simul routine, containing routine calls for each VHDL process, namely for P1 and P2. The basic blocks b38 and b42 contain an instruction simul if that represents the guards for the sensitivity list evaluation. The basic block b49 containing the instruction simul\_wait is the so called synchronization point. Here, the signal assignments take effect and we can decide whether a signal value has changed compared with the previous iteration. In Figure 1 there is another call instruction not mentioned so far, the simul\_call\_environment that calls the routine environment. We need this routine for

In Figure 1 there is another call instruction not mentioned so far, the simul\_call\_environment that calls the routine environment. We need this routine for analyzing open systems, which roughly are systems that have external input signals. These signals have to be set somewhere in the environment of the system modeled by the VHDL description and they drive the behavior of the whole system. One intuitive example for such an external signal is the reset signal.

#### 4.3 Modeling the clock

If we want to analyze synchronous designs, i.e. systems that are synchronized with either the rising or the falling edge of the clock signal, we need to model this signal somehow. Unfortunately the synthesizable subset of the VHDL standard [11] does not enable us to model a clock signal<sup>8</sup>.

<sup>&</sup>lt;sup>8</sup>In synthesizable VHDL, there are two main restrictions: a process can not be sensitive on a signal it drives and there is no possibility to wait for a timeout. Thus, there is no construct left for modeling the frequent change of a clock signal.

Despite this, we can simulate the clock easily by introducing a new routine, called clock, that calls the routine simul twice. Before one call the clock signal is set to one and before the other call the clock signal is set to zero. This makes our approach rather flexible as we can analyze synchronous designs as well as asynchronous ones.

#### 5 Example: Constant Propagation

This sections describes, how the framework introduced in Section 4 can be used to model a constant propagation analysis on VHDL.

A constant propagation analysis determines for each program point, i.e. each statement, if a signal or variable has a constant value, when execution reaches that point. To model this, we introduce a mapping from identifier names to their corresponding value and extend it by the usual bottom and top elements to denote not yet considered program points and unknown values respectively.

$$F \equiv (identifier \rightarrow (value \cup \top)) \cup \bot$$

As stated in Section 3, VHDL differs between signal and variable assignments. Thus, the domain of the data flow problem for constant propagation analysis has to cover *current* and *future* values of the identifiers used. Furthermore, to evaluate the condition of process guards (simul\_if, see Section 4.2), it is necessary to decide, whether a signal has changed its value or not. Therefore, the domain has to be extended by the *old* values of signals. Thus, the domain *dfi* for the constant propagation analysis is:

$$dfi \equiv F \times F \times F$$

The transition functions for updating an incoming data flow value  $dfi_{pre} = (cur_{pre}, fut_{pre}, old_{pre})$  to the output value  $dfi_{post}$  for the different nodes can be directly defined as follows:

#### • assignment node

The data flow value for an assignment can be computed from the incoming value in case of a variable assignment by updating the current and the future value of  $df_{pre}$  with the newly assigned value or  $\top$ , if this value is statically not computable. In case of a signal assignment, only the future value has to be updated.

#### • simul\_if node

The guard encapsulates the sensitivity list of a process and is responsible for the repeated execution of it. A process is only re-executed, if one of the signals in its sensitivity list changes its value. This can be checked by comparing  $cur_{pre}$  with  $old_{pre}$ . Based on this result, the data flow value is propagated into the process or not.

#### • sync node

At this node, all scheduled signal assignments take effect and are made visible at once. The new data flow

value is computed by copying the future values to the current one and the current ones to the old ones.

$$dfi_{post} = (fut_{pre}, fut_{pre}, cur_{pre})$$

#### • environment node

Writing a special rule for this node allows us to analyze the VHDL code with respect to special system criteria. E.g., if we want to analyze the reset behavior of the code displayed in Figure 2, we introduce a rule  $cur_{post} = cur_{pre} \setminus [rst \rightarrow 0]$  and  $fut_{post} = fut_{pre} \setminus [rst \rightarrow 1]$  always setting the current and future value of rst to 0 and 1 respectively. This yields to the perception, that cnt and therewith val have constant values during reset.

Using PAG and the rules above yields in a constant propagation analysis on VHDL. The results can now be used for further analyzes and transformations of the VHDL code as described in Section 7.

#### 6 Experiments

Despite the example given in the previous section, we successfully tested our implementation with the complete VHDL specification of the Leon2 processor core [7]. The Leon2 is a synthesizable VHDL model of a 32-bit processor compliant with the SPARC V8 architecture with a 5-stage pipelined integer unit, data and instruction cache, hardware multiply, divide and MAC units. The model is highly configurable, and particularly suitable for system-on-a-chip (SOC) designs. The VHDL specification of the Leon2 consists of more than 80 modules containing about 75.000 lines of code.

#### 7 Outlook

The analysis framework described in this paper is only one part of a much bigger task: The semi-automatically derivation of timing analyzers from a formal processor specification

With the work here, we are able to read VHDL specifications and to perform static analyzes like constant propagation on it. This eases the task of finding suitable abstractions for a processor model, i.e. cropping the model to the parts that are only relevant for the timing behavior.

As noted earlier, a VHDL design is too large to be used directly in timing analysis, thus we have to throw away things not influencing the timing. This can be achieved by slicing backwards from the place, where instructions leave the pipeline, i.e. finish execution. Only external signals and variables or those being assigned to in the slice can influence timing. Signals and variables used (i.e. read) but not assigned in the slice do not change their values (i.e. have fixed values) and can be omitted.

<sup>&</sup>lt;sup>9</sup>Successfully here means, that we are able to create static analyzers based on analysis specifications.

Even after this removal, the model may be too large for timing analysis. Thus, we approximate concrete components by abstract ones (see [6] for more details) which are smaller in size. An example can be found in [5].

For this, we want to develop support tools to incorporate transformations on the VHDL model based on the analysis results semi-automatically in order to derive abstract models.

From an abstract processor model, we need to generate a C-code analysis fitting into the tool chain of the *aiT* tool. At the end of the story, we want to derive a timing analyzer from a formal hardware specification. This not only speeds up the task a creating such a timing analysis but additionally the generated analyzer is already validated due to the derivation from the hardware specification.

#### 8 **Conclusions**

Safety-critical applications as for example the flight control software in avionics or the airbag control software in the automotive industry are underlying hard real-time constraints. Therefore the computation of the worst-case execution time (WCET) is the key issue for guaranteeing that a system satisfies its timing boundaries.

The growing complexity of modern processor architectures used within such safety-critical systems complicates the task of creating a sound timing analysis. Currently, these analyzes are based on hand-crafted abstract processor models. But this is a very time consuming and error-prone process.

To ease the task of finding suitable abstractions, we introduced a framework for static analyzes of formal processor descriptions in VHDL. By transforming the VHDL model into a sequential program, we can generate static analyzers from a concise specification using the *Program Analyzer* Generator [14]. Our framework is very flexible because we can analyze open designs as well as closed ones, i.e. systems that does or does not depend on external driven signals respectively.

By using CRL2 as the intermediate representation, we can combine several analyzes. This means that an analysis can use the result of another one because the results are annotated as attributes in our intermediate representation.

To illustrate the practicability of our framework, we showed how to create a constant propagation analysis on a VHDL description of a 3-bit counter.

In [9, 10] Charles Hymans gives a design for static analysis of VHDL that uses abstract interpretation. Despite this and to the best of our knowledge, our work presented here is the first work concerning a framework for generating static analyzers on VHDL code. Our results are currently going to be used for the semi-automatically derivation of timing analyzers from a formal processor description in VHDL.

#### Acknowledgments

This work was partly supported by the German Research Council (DFG) as part of the Transregional Collaborative Research Center "Automatic Verification and Analysis of Complex Systems" (SFB/TR 14 AVACS) and by EU network of excellence IST-004527 ARTIST2 on Embedded Systems Design.

#### References

- [1] AbsInt Angewandte Informatik GmbH. The Program Analyzer Generator User's Manual, 2002.

- P. J. Ashenden. The Designer's Guide to VHDL. Morgan

- Kaufmann Publishers Inc., San Francisco, CA, USA, 2001.

[3] P. Cousot and R. Cousot. Abstract interpretation: A unified lattice model for static analysis of programs by construction or approximation of fixpoints. In POPL, pages 238-252,

- [4] P. Cousot and R. Cousot. Abstract interpretation and application to logic programs. J. Log. Program., 13(2-3):103-179,

- [5] C. Ferdinand. Cache Behavior Prediction for Real-Time Sys-

- tems. PhD thesis, 1997. [6] C. Ferdinand, F. Martin, C. Cullmann, M. Schlickling, I. Stein, S. Thesing, and R. Heckmann. New Developments in WCET Analysis. In T. Reps, M. Sagiv, and J. Bauer, editors, Program Analysis and Compilation. Theory and Practice., volume 4444 of LNCS, pages 12-52. Springer, 2007.

- [7] J. Gaisler. Leon2 Processor User's Manual Version 1.0.30, July 2005.

- [8] R. Heckmann, M. Langenbach, S. Thesing, and R. Wilhelm. The Influence of Processor Architecture on the Design and the Results of WCET Tools. Proceedings of the IEEE, 91(7), July 2003.

- [9] C. Hymans. Checking safety properties of behavioral vhdl descriptions by abstract interpretation. In SAS, pages 444-460, London, UK, 2002. Springer.

- [10] C. Hymans. Design and implementation of an abstract interpreter for vhdl. In D. Geist and E. Tronci, editors, CHARME, volume 2860 of LNCS. Springer, 2003.

- [11] Institute of Electrical and Electronics Engineers, New York. IEEE Standard P1076.6 1999 VHDL Register Transfer Level Synthesis, 1999.

- [12] Institute of Electrical and Electronics Engineers, New York. IEEE Standard P1076 2000 VHDL Language Reference Manual, 2000.

- [13] M. Langenbach. CRL A Uniform Representation for Control Flow. Technical report, 1998.

- [14] F. Martin. Generating Program Analyzers. PhD thesis, Saarland University, 1999

- [15] F. Martin, M. Alt, R. Wilhelm, and C. Ferdinand. Analysis of Loops. In K. Koskimies, editor, CC, volume 1383 of LNCS. Springer, 1998

- [16] F. Nielson, H. R. Nielson, and C. Hankin. Principles of Program Analysis. Springer, 1999.

- [17] M. Sharir and A. Pnueli. Two approaches to interprocedural data flow analysis. Prentice-Hall, 1981.

- [18] S. Thesing. Safe and Precise WCET Determinations by Abstract Interpretation of Pipeline Models. PhD thesis, Saarland University, 2004.

- [19] S. Thesing. Modeling a System Controller for Timing Analysis. In *EMSOFT*, pages 292–300, 2006.

#### **Analysing Switch-Case Tables by Partial Evaluation**

Niklas Holsti

## Tidorum Ltd Tiirasaarentie 32, FI 00200 Helsinki, Finland niklas.holsti@tidorum.fi

#### **Abstract**

Tracing the flow of control in code generated from switch-case statements is difficult for static program analysis tools when the code contains jumps to dynamically computed target addresses. Analytical methods such as abstract interpretation using integer intervals can work for some forms of switch-case code, for example a jump via a table of addresses indexed 1 .. n, but fail when the target compiler encodes the switch-case structure in a ROM table with a complex format and uses a library routine to interpret the table at run-time.

This paper shows how to extract the flow of control from such switch-case tables by partial evaluation of the table-interpreting routine. The resulting control-flow graph allows accurate analysis of the execution time and the logical conditions for reaching each case in the switch-case statement.

The method is implemented in Tidorum's Bound-T tool for worst-case execution-time analysis. The implementation builds on some basic Bound-T features for modeling program states in the flow-graph and propagating constant values through the graph.

#### 1. Introduction

Static analysis of the worst-case execution time (WCET) of a program usually begins by building the control-flow graph (CFG). On the machine code level, where most WCET tools work, the tool has to find the possible successor instructions of each instruction under analysis. This is easy when the instruction defines its successors statically but hard for control-transfer instructions with dynamic target addresses, for example register-indirect jumps. Such dynamic transfer of control (DTC) instructions often result from switch-case statements [1, 6, 8].

The switch-case statement in languages such as C or Ada is a very flexible control structure. The programmer can choose the type of the switch index, for example an 8-bit or a 32-bit number; whether the cases are numbered densely  $1 \dots n$  or are a sparse subset of a large range; whether each case is reached by a unique index value or by a set or range of values; and whether there is a default case or not. Compilers often generate quite different

kinds of code to implement different kinds of switch-case statements.

For small target processors such as the Intel 8051 or Atmel AVR some compilers try to reduce code size by encoding the switch-case statement into a ROM *switch table* and generating a call or jump to a *switch handler* routine that interprets the table at run-time. There may be several types of switch table, for example depending on the index type, each with its own switch handler.

This paper describes a way to find the full control-flow graph for code that uses switch tables and switch handlers. Section 2 defines a particular switch-table structure and the corresponding switch handler for use in examples. Section 3 states the problem and the goals for the solution. Section 4 defines the suggested solution as a form of partial evaluation. Sections 5 and 6 explain how this solution is implemented in the Bound-T WCET tool [2] and section 7 shows an example. Section 8 summarises the analysis method. Sections 9 and 10 report experience from implementation and experiments, respectively. Section 11 discusses related earlier work and section 12 concludes the paper.

When discussing the Bound-T implementation I will use the term "flow-graph" instead of the usual "control-flow graph". Section 5 explains why.

#### 2. Example of switch table and handler

The switch-table structure in this example was chosen to make the switch handler brief but not trivial. The structure is not taken directly from any compiler that I know of but is similar to real switch tables for 8-bit processors. The structure assumes a type of Atmel AVR processor with a 16-bit program counter and at most 64 KB of program memory.

In this example a switch table is a sequence of *entries*. An entry represents a set of 8-bit switch-index values that lead to the same case in the switch-case statement. An entry consists of four octets: a *mask* octet, a *match* octet, and the low and high octets of the 16-bit *address* for the case to be taken when the bit-wise logical "and" of the switch index and the *mask* octet equals the *match* octet. The order of entries in the table is arbitrary but the last entry always has a zero *mask* and *match*. This

represents the default case if there is one, else fall-through to the statement after the switch-case.

Consider this C subprogram foo:

```

void foo (unsigned char k)

{

switch (k) {

case 4:

<statements for k = 4>

case 8: case 9: case 11:

<statements for k = 8, 9 or 11>

default:

<statements for other values of k>

}

}

```

The switch table for this switch-case statement is shown in Table 1 below. It has four entries for a total size of 16 octets. Note that the second entry matches both k=8 and k=9 because the mask value 254 masks the least significant bit of k.

#### Listing 1. Example switch handler SwHandler: ; Switch-case handler. Entered by call with the ; switch index in r0 and the switch table in ; program memory after the call instruction. Exits ; to the chosen case. Changes r1, r2, and Z. 0100 pop ; low octet of table address r30 ; high octet of table address 0101 pop r31 ; Z = r31:r30 = word address of the switch table. 0102 add r30,r30; Multiply Z by two to make 0103 adc r31,r31; it an octet address for lpm. ; Z points at the next switch table entry. loop: 0104 lpm r1,Z+ ; r1 := entry.mask0105 lpm ; r2 := entry.matchr2,Z+ ; r1 := index and mask0106 and r1,r0 0107 cp ; compare to entry.match r1,r2 0108 breq found ; branch if entry matches index 0109 adiw Z,2 ; no match, point at next entry 010A rjmp loop ; try next entry *Entry matches. Z points at entry.address.* found: ; r1 := address low octet010B lpm r1,Z+ ; $r31 := address \ high \ octet$ 010C lpm r31,Z Z := whole address010D mov r30,r1 010E ijmp ; DTC jump to address in Z.

# In this example a switch-case statement is compiled into code that loads the switch index (the parameter k in foo) into register r0 and calls the switch handler SwHandler. The switch table is placed in the program memory immediately after the call so that the return address points to the first table entry. SwHandler searches the table for an entry that matches the switch index, then jumps to the address of this entry.

SwHandler can be written in AVR assembly language [3] as shown in Listing 1 below. For later reference the left margin shows the assumed word address of the instruction (in hex). Semicolons start comments that extend to end of line.

Listing 2 below shows the AVR code for function *foo* including the code for the switch-case statement and the hex form of the switch table. Listing 2 assumes that k is passed to *foo* in register r16 and some arbitrary amounts of code in the case branches.

| Table 1. Example switch table |                               |                                         |  |

|-------------------------------|-------------------------------|-----------------------------------------|--|

| mask                          | mask match address points to: |                                         |  |

| 255                           | 4                             | the code for the case $k = 4$           |  |

| 254                           | 8                             | the code for the case $k = 8$ , 9 or 11 |  |

| 255                           | 11                            | the code for the case $k = 8$ , 9 or 11 |  |

| 0                             | 0                             | the code for the default case           |  |

```

Listing 2. Example switch-case statement code

foo:

; r0 := k

0200 mov

r0,r16

0201 call SwHandler

; The switch table consists of the following

; 16 octets, shown in hex:

0203 FF 04 0B 02

k = 4, address = 020B

0205 FE 08 1C 02

k = 8 \text{ or } 9, \text{ address} = 021C

k = 11, address = 021C

0207 FF 0B 1C 02

; default, address = 0224

0209 00 00 24 02

020B < code for the case k = 4 >

021C < code for the case k = 8, 9 or 11 >

0224 < code for the default case >

0229 ret

; return from foo.

```

#### 3. Problem and goals

The problem is to find the full control-flow graph for machine code that uses switch tables and switch handlers, for example with the structure described in section 2 but of course not limited to that example. The machine code is given as a memory image that is a mixture of code and data, not clearly demarcated. The solution should:

- find all cases of all switch-case statements,

- *not* mix up different switch-case statements to create false paths in the flow-graph,

- produce the sequence of instructions that leads to each case, so that later steps in the analysis can find an accurate WCET for each case,

- connect each case with the corresponding values of the switch index, again for use in later analysis steps (for example to find bounds for a loop that is nested in a case and depends on the switch index),

- apply uniformly to several kinds of switch tables and handlers and be robust to changes in their structure as the compilers evolve.

The solution should also be easy to implement in the generic, processor-independent parts of a WCET tool, in my case Bound-T [2], with minimal changes to the processor-specific parts, for example the parts of Bound-T that decode AVR instructions.

Bound-T can analyse many aspects of a subprogram in a (calling-) context-dependent way but the flow-graph of a subprogram must be independent of context. Analysing a switch handler (for example SwHandler) as an ordinary, independent subprogram cannot give a context-dependent resolution of the DTC (the *ijmp* in SwHandler). Instead, a switch handler must be analysed as an integral part of the subprogram that contains the switch-case statement (for example foo). This is similar to in-line expansion of the call to the switch handler.

The target addresses for the DTC result from executing the switch-handler instructions that access the switch table. The analysis must thus simulate or execute these instructions. Furthermore, the analysis must unroll the table-scanning loop in the switch handler. Each iteration of the loop leads to a different case; unrolling the loop separates the paths to the different cases for separate analysis.

#### 4. The solution by partial evaluation

Partial evaluation is the execution of a program with some inputs bound to concrete values but other inputs not so bound (free input variables) [4]. The result is therefore not a concrete output value but a residual program that still depends on the unbound inputs. The residual program is a specialization of the original program: it is specialized to the domain where the bound inputs have the given values.

The proposed analysis of switch tables and switch handlers uses partial evaluation of subprograms as follows. A switch handler is a subprogram with two inputs: the switch index and the switch table. At analysis time, in a given invocation of a switch handler for a given switch-case statement the switch index is usually unbound (has an unknown, dynamic value) but the switch table is bound to a static constant: the table generated for this switch-case statement.

If we partially evaluate the switch handler under this binding, the residual subprogram depends only on the switch index and not on the switch table. The partial evaluation resolves the DTC instructions into control transfers with static target addresses, copied or computed from the switch table.

For the switch handler shown in section 2 partial evaluation with a known switch table means that we know the value loaded by the execution of any *lpm* instruction. Thus the target address of each possible execution of the *ijmp* DTC instruction is known even if the value of the switch index (r0) is unknown.

Within the Bound-T tool the partial evaluation is implemented in a way that fits the Bound-T architecture, not as a general-purpose partial evaluator such as the *mix* evaluator described in [4]. In Bound-T the original, unevaluated subprogram (the

switch handler) is represented implicitly by its entry address and the instructions in the target program that can be reached from the entry address. The residual subprogram (the switch handler specialized to a given switch table) is represented as a part of the flow-graph of the subprogram that contains the switch-case statement. This part is a subgraph rooted at the node that invokes the switch handler. The nodes of the subgraph represent (executions of) instructions in the switch handler; the leaves of the subgraph represent the DTC leading to each case.

In the terminology of [4] the *source language* of this partial evaluator is machine-code programmemory images and the *target language* is Bound-T flow-graphs. (As a part of Bound-T the *implementation language* is Ada, but this is not important.)

The next two sections explain how partial evaluation is implemented in Bound-T and why it is a natural extension of the way in which Bound-T builds flow-graphs from machine code. This says more about Bound-T than about the partial evaluation method for switch-case analysis. Eager readers may skip to section 7 for an example of the analysis.

#### 5. Building flow-graphs in Bound-T

This section describes the structure of flow-graphs in Bound-T and the iterative algorithm for building flow-graphs from machine code. The next section extends the algorithm to include partial evaluation.

First a definition of terms. The internal representation of a subprogram in Bound-T is a *flow-graph* (FG). A flow-graph differs from a control-flow graph (CFG) because (as defined in this paper) a CFG node represents a given machine instruction in *any* program state while an FG node represents a given instruction in some *subset* of program states. Thus, a given instruction is always represented in at most one CFG node, but can be represented in several FG nodes when this instruction is modeled separately for different program states. Bound-T adopted the flow-graph concept to model complex control mechanisms such as nested zero-overhead loops in DSPs.

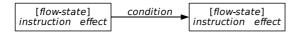

The abstraction of the program state that is used for flow-graphs is called the *flow-state*. The program counter (PC) is always a concrete part of the flow-state; a flow-state implies a PC value. Each node in a flow-graph is *tagged* with a flow-state. No other node in this flow-graph is tagged with this flow-state.

Each flow-graph node has several attributes to model the instruction in this node. For this paper the main attribute is the *computational effect*: a set of assignments of expressions to variables (registers or memory locations). For example, the effect of the AVR instruction  $lpm\ r1, Z+$  is modeled by the assignments  $r1:=pm[Z],\ Z:=Z+1$  where pm[Z] stands for the value of the program memory octet at address Z. (Ignore the fact that the 16-bit Z pointer is composed of the two 8-bit registers r30 and r31. This complication is nasty but not relevant here.)

Each edge in the flow-graph is provided with a Boolean expression that is a necessary but perhaps not sufficient *condition* for taking this edge. For example, the condition for the branch-taken edge after the AVR instruction breq is that the "zero" flag be set, here written as zf = 1. The condition is evaluated after the effect of the source node.

Bound-T starts the analysis of a subprogram by building the flow-graph of the subprogram. This is an iterative algorithm very like the algorithm in [6]. For each new flow-state the algorithm first adds a blank node to the flow-graph and then proceeds to fill in the blank nodes with their attributes. The final flow-graph contains all flow-states and instructions in the subprogram that can be reached from the entry address. The algorithm follows.

#### Building the flow-graph of a subprogram in Bound-T

*Initialization*. The flow-graph is initialized to consist of one blank node tagged with the flow-state that represents the entry address of the subprogram.

*Iteration*. The algorithm repeatedly executes the *Fill node* step until there are no blank nodes in the flow-graph.

Fill node. Pick a blank node N from the flow-graph. The flow-state of the node identifies (through its PC value) the instruction executed in this state. Fetch this instruction from the memory image of the target program and fill in the attributes of node N from this instruction.

Determine all successor flow-states for node *N*. The successor of a normal call instruction is the return point in the caller. A normal return instruction has no successors.

For each successor state s of N, if there is not already a flow-graph node S tagged with s then add such a new blank node S to the flow-graph. Make a new edge from N to S

The analysis of normal subprogram calls in Bound-T is not relevant to this paper because a call to a switch handler will be analysed as if the call were *in-lined*. A switch-handler call is analysed as a kind of jump instruction by a simple variation of the above algorithm: the successor of a call to a switch handler is taken to be the first instruction in the switch handler, instead of the return point in the callee.

For the example in section 2 the return point contains the switch table, not AVR instructions, so control never reaches the return point.

#### 6. Partial evaluation in Bound-T

This section explains how the flow-state concept was extended to implement partial evaluation during flow-graph building in Bound-T.

First note that the flow-graph building algorithm can already be viewed as partial evaluation. The entry address (initial PC value) is one input for the target program; building the flow-graph amounts to partial evaluation of the target program with respect to this input, keeping all other inputs unbound. The partial evaluation of an instruction amounts to finding the effect of the instruction on the PC, in other words finding the successor instructions.

We can extend this partial evaluation simply by adding more concrete state components to the flow-state. Of course, this forces us to compute the effect of each instruction on these new flow-state components to find the successor flow-states of the instruction.

To implement this in Bound-T the flow-state type is extended with a *data-state* component that is either null or a pointer to a *data-state object*. A data-state object models the values of program variables just before executing the node tagged with this data-state.

For this paper a data-state object is a *partial mapping of variables to values*. In other words a data-state binds some variables to known values but leaves all other variables unbound. For example, the data-state on entry to *SwHandler* from the call in *foo* could bind the variable holding the return address (the top stack word) to the value 0203 (hex) and leave all other variables unbound.

The flow-graph building algorithm is extended to handle data-states as follows. When partial evaluation is not in progress the data-state is null and the algorithm works as before. Otherwise the algorithm uses the data-state to partially evaluate the computational effects and edge conditions and uses the residual effects and conditions to update and propagate the data-state over nodes and edges.

#### Handling data-states while building the flow-graph

When filling a node for a given flow-state. If the given flow-state has a non-null data-state, partially evaluate the computational effect of the node on this data-state and store the *residual* effect in the node. Also create the *post-state* of the node as the given data-state updated by the residual effect: assignment of a constant binds the target variable, other assignments unbind it. The post-state models the program state *after* executing the instruction in this node.

If the given flow-state has a null data-state make the post-state null too.

When adding an edge from a source node to a successor flow-state. If the post-state of the source node has a non-null data-state, partially evaluate the given edge condition on this data-state and if the result is false discard the edge as infeasible. Otherwise store the residual condition in the edge. If the successor flow-state has a specified data-state (whether null or not) use it as such (this happens when starting or stopping partial evaluation). Otherwise use the post-state of the source node but constrained by the residual edge condition: if the condition implies a known value for a variable then update the successor data-state with this binding.

When filling a DTC node. If the node has a non-null datastate then try to compute the target address from the data-state. If this succeeds (ie. if the DTC target depends only on variables bound to constants in the data-state) then add the corresponding (static) edge; also, if this DTC represents an exit from a switch handler then put a null data-state in the target of the new edge, to stop partial evaluation on this path.

The extensions to the algorithm use existing Bound-T services for propagating constant values in flow-

graphs and computational effects. New code was needed mainly for the container of data-state objects.

Most of the extensions for data-state handling are implemented in the processor-independent parts of Bound-T. The processor-specific modules only have to start and stop the partial evaluation at suitable points in the analysis. For this paper I assume that the processor-specific modules detect when a call or jump instruction enters a switch handler; at that point these modules start partial evaluation by putting the initial data-state for the switch handler in the target of the edge that enters the switch handler. Likewise, I assume that processor-specific modules detect when a DTC is an exit from a switch handler. Section 8 discusses these assumptions.

#### 7. Example

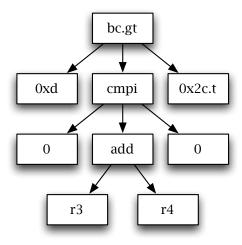

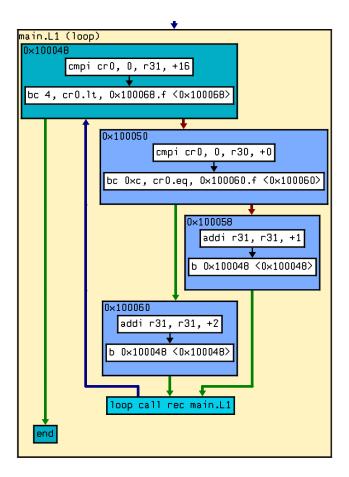

This section shows how the partial evaluation works for the *foo* function and the *SwHandler* from section 2 by a series of snapshots of the growing flow-graph.

Nodes and edges in the flow-graph are drawn as follows:

The flow-state is shown in brackets [] at the top of the box that depicts a node. The flow-state starts with the instruction address (PC) in hex, followed by the data-state bindings if any. For brevity only relevant bindings are shown. The AVR instruction is shown below the flow-state, followed by the relevant parts of its residual computational effect. An edge with no condition is unconditional (always taken). Blank nodes are shown as a bare "[flow-state]" with no box.

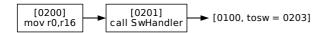

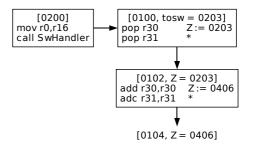

The first figure below shows the flow-graph of *foo* after the first two instructions are inserted (with null data-states) and just after detecting that the second instruction (the call) enters a switch handler. The AVR-specific modules of Bound-T have accordingly defined the successor of the call to be the first instruction in SwHandler (PC = 0100 hex) with a data-state that binds the return address (top of stack word, tosw) to 0203 hex. There is one blank node with this flow-state [0100, tosw = 0203].

As the flow-graph grows I will compress the figures by showing several successive instructions in one box.

The next figure shows the flow-graph when the first four instructions from *SwHandler* have been inserted. Note how the partial evaluation of the *pop* instructions transformed the *tosw* binding into a binding for the *Z* pointer and how the evaluation of the *add* and *adc* instructions doubled the value bound to *Z*. (The asterisks indicate a computational effect that was combined with a preceding instruction to

build a 16-bit operation from two or more 8-bit operations.) The single blank node shows that the next instruction to be added is the first instruction in the loop in *SwHandler*, at address 0104, with a data-state binding *Z* to 0406 hex, the octet address of the first entry in the switch table.

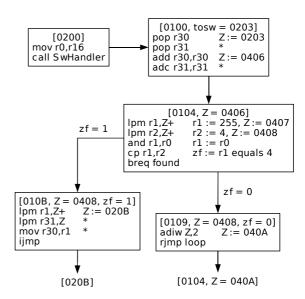

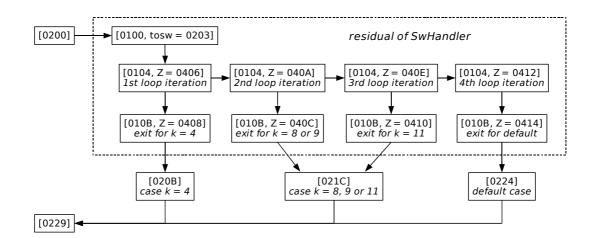

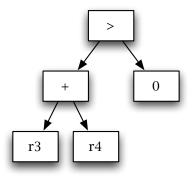

The next figure shows the flow-graph when it contains all the loop instructions and the first possible exit from the loop (for k=4). On the left the loop exits when zf=1. The ijmp DTC is resolved to a static jump because the data-state binds Z to 020B hex. This identifies the first case of the switch. Partial evaluation in this branch stops because the successor flow-state [020B] has a null data-state.

On the right, when zf = 0, the loop is about to repeat ( $rjmp\ loop$ ). The successor flow-state contains the address of the loop-head (0104) which is already represented by a filled node, but it has a different data-state: Z is bound to 040A, not 0406 as in the existing node. The algorithm therefore creates new nodes for the second iteration of the loop. In fact the loop will be fully unrolled because the data-state binds Z to a different value in each iteration of the loop.

The third loop iteration is unrolled in the same way. The figure below shows the flow-graph parts for the fourth iteration which accesses the last switch-table entry (the default case) at octet address 0412 (word address 0209). The loop-repeating edge with the original condition zf = 0 becomes infeasible because the data-state binds zf to 1, making the residual con-

dition *false*. This ends the unrolling and also the partial evaluation.

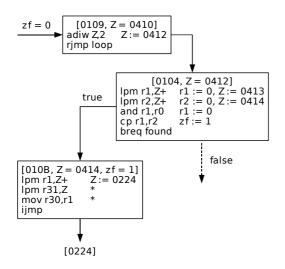

The last and largest figure, below, is an overview of the final flow-graph of *foo*. The residual form of *SwHandler* within this flow-graph is a tree of com-

parisons and conditional branches that explicitly models the sequence of instructions leading to each case. The edge conditions (not shown in the figure) define the corresponding index values.

#### 8. Summary

To summarise, this method for finding the flow of control encoded in switch tables comes in three parts:

- 1. A flow-graph structure that can model the same instruction separately in different states (the flow-state in Bound-T).

- 2. A state abstraction and transfer functions for data values (the data-state and computational effects in Bound-T).

- 3. Means to detect entry to and exit from a switch handler in order to start/stop partial evaluation.

The first two points enable partial evaluation of machine code into parts of flow-graphs. The third point applies partial evaluation to reveal the flow of control in switch tables.

This partial-evaluation method largely achieves the goals listed in section 3. The two main problems left are processor-specific. The first problem is to model the computational effects of all instructions so exactly that the partial evaluation of the switch handler resolves the DTCs. For example, no version of Bound-T now models the "half carry" flag for BCD arithmetic. If a switch handler uses this flag in a DTC the partial evaluation will not resolve the DTC.