6<sup>th</sup> International Workshop on Operating Systems Platforms for Embedded Real-Time Applications (OSPERT 2010)

in Conjunction with the 22<sup>nd</sup> Euromicro Conference on Real-Time Systems (ECRTS 2010)

July 6, 2010, Brussels, Belgium

POLITÉCNICO DO PORTO

**Kill** Edições Stefan M. Petters and Peter Zijlstra (Editors)

# International Workshop on Operating Systems Platforms for Embedded Real-Time Applications

Workshop Proceedings

# **Table of Contents**

- 4 Message from the Chairs

- 4 Program Committee

- 5 Workshop Program

- 6 Dual Operating System Architecture for Real-Time Embedded Systems

- 16 Timeslice Donation in Component-Based Systems

- 24 Full Virtualization of Real-Time Systems by Temporal Partitioning

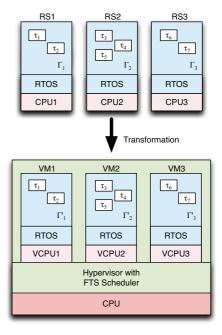

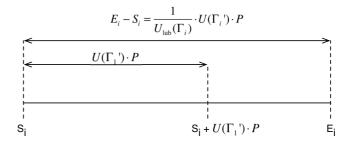

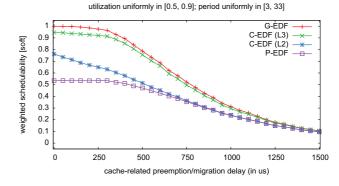

- 33 Cache-Related Preemption and Migration Delays: Empirical Approximation and Impact on Schedulability

- 45 Implementation of Overrun and Skipping in VxWorks

- 53 Schedulable Device Drivers: Implementation and Experimental Results

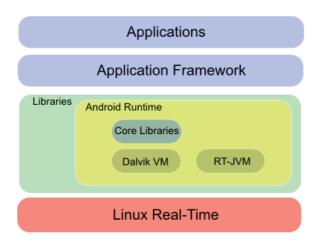

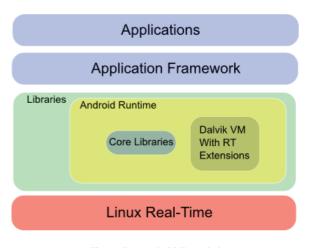

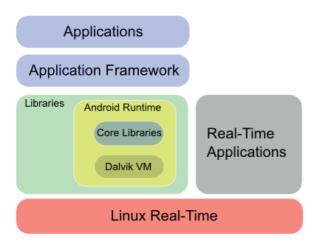

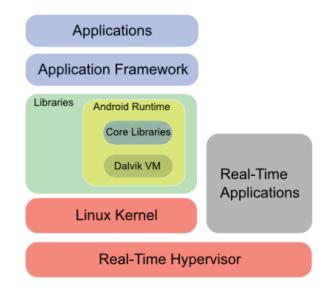

- 62 Evaluating Android OS for Embedded Real-Time Systems

- 70 Extending an HSF-enabled Open Source Real-Time Operating System with Resource Sharing

- 81 Implementation and Evaluation of the Synchronization Protocol Immediate Priority Ceiling in PREEMPT-RT Linux

- 91 The Case for Thread Migration: Predictable IPC in a Customizable and Reliable OS

# Editors: Stefan M. Petters Peter Zijlstra

Copyright 2010 Politécnico do Porto.

All rights reserved. The copyright of this collection is with Politécnico do Porto. The copyright of the individual articles remains with their authors.

# Message from the Workshop Chairs

It has been a pleasure to serve again in the preparation of this year's Workshop on Operating Systems Platforms for Embedded Real-Time Applications. Again we aimed for an interactive format in the workshop providing a discussion forum for novel ideas as well as the interaction between academics and practitioners. To enable this we have looked at providing ample of discussion time both in between paper presentations as well as in the dedicated discussion slots.

Obviously such endeavours are not the result of one or two individuals working, but are the product of many helping hands. The first thanks goes to Gerhard Fohler for trusting us in our second go at this Workshop.

At the start of the day and after lunch between the discussion sessions we have scheduled three paper presentations sessions. The 10 papers presented were selected out of a total of 16 submissions. We thank all the authors for their hard work and submitting it to the workshop for selection, the PC members and reviewers for their effort in selecting an interesting program, as well as the presenters for ensuring that this will be an entertaining and informative day.

Last, but not least, we would like to thank you, the audience, for your attendance. A workshop lives and breathes because of the people asking questions and contributing opinions throughout the day.

We hope you will find this day interesting and enjoyable.

The Workshop Chairs

Stefan M. Petters Peter Zijlstra

# **Program Committee**

David Andrews, University of Arkansas Fayettville, USA Neil Audsley, University of York, UK Peter Chubb, NICTA, Australia Steve Goddard, University of Nebraska Lincoln, USA Hermann Härtig, TU Dresden, Germany Johannes Helander, Microsoft, Germany Robert Kaiser, University of Applied Sciences Wiesbaden, Germany Tei-Wei Kuo, National Taiwan University, Taiwan Stefan M. Petters, IPP-Hurray, Portugal Peter Zijlstra, Red Hat, Netherlands

# Program:

09:00-10:30 Session 1: Virtualisation

**Dual Operating System Architecture for Real-Time Embedded Systems** Daniel Sangorrin, Shinya Honda, and Hiroaki Takada; *Nagoya University, Japan*

**Timeslice Donation in Component-Based Systems** Udo Steinberg, Alexander Böttcher, and Bernhard Kaue; *TU Dresden, Germany*

**Full Virtualization of Real-Time Systems by Temporal Partitioning** Timo Kerstan, Daniel Baldin, and Stefan Groesbrink ; *Univerisy of Paderborn, Germany*

10:30-11:00 Coffee Break

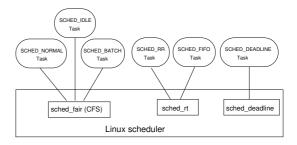

11:00-12:30 Session 2: Panel Discussion Linux Scheduler Meet Real-Time 12:30 -13:30 Lunch

13:30-15:30 Session 3: Implementation and Analysis

Cache-Related Preemption and Migration Delays: Empirical Approximation and Impact on Schedulability

Andrea Bastoni, Björn B. Brandenburg, and James H. Anderson; University of North Carolina at Chapel Hill, USA

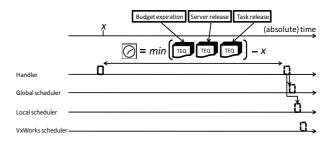

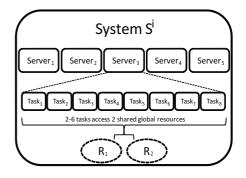

# Implementation of Overrun and Skipping in VxWorks

Mikael Åsberg, Moris Behnam, Thomas Nolte, and Reinder Bril; *Maelardalen RTC, Sweden and TU Eindhofen, Netherlands*

## Schedulable Device Drivers: Implementation and Experimental Results

Nicola Manica, Luca Abeni, Luigi Palopoli, Dario Faggioli, and Claudio Scordino; University of Trento, Scuola Superiore S. Anna, and Evidence Srl, Italy

# **Evaluating Android OS for Embedded Real-Time Systems**

Cláudio Maia, Luís Nogueira, and Luís Miguel Pinho; Polytechnic Institute of Porto, Portugal

15:30-16:00 Coffee Break 16:00-17:30 Session 4: Resource Sharing and Communication

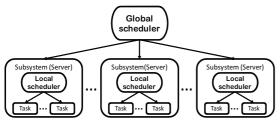

**Extending an HSF-enabled Open Source Real-Time Operating System with Resource Sharing** Martijn M.H.P. van den Heuvel, Reinder J. Bril, Johan J. Lukkien, and Moris Behnam; *TU Eindhofen, Netherlands and Maelardalen RTC, Sweden*

# Implementation and Evaluation of the Synchronization Protocol Immediate Priority Ceiling in PREEMPT-RT Linux

Andreu Carminati, Rômulo Silva de Oliveira, Luís Fernando Friedrich, and Rodrigo Lange; Federal University of Santa Catarina, Brazil

**The Case for Thread Migration: Predictable IPC in a Customizable and Reliable OS** Gabriel Parmer; *George Washington University, USA*

17:30-18:00 Session 5: Group Discussion Wrap up and lessons learned

# **Dual Operating System Architecture for Real-Time Embedded Systems**

Daniel Sangorrin, Shinya Honda and Hiroaki Takada

Graduate School of Information Science, Nagoya University, Japan {dsl,honda,hiro}@ertl.jp

#### Abstract

Virtualization architectures for the combination of realtime and high-level application tasks, on the same embedded platform, pose special reliability and integration requirements compared to solutions for the enterprise domain. This paper presents a software architecture to execute concurrently, on a single processor, a real-time operating system (RTOS) and a general-purpose operating system (GPOS). The proposed approach, based on common embedded security hardware (ARM TrustZone<sup>®</sup>), enables integrated scheduling of both operating systems to enhance the responsiveness of the GPOS soft real-time tasks and interrupts while preserving the determinism of the RTOS and without modifications to the GPOS core. The presented architecture has been implemented and evaluated on real hardware. Its low overhead and reliability makes it suitable for embedded applications such as car navigation systems, mobile phones or machine tools.

## 1. Introduction

In recent years, methods for integrating real-time control systems and high-level information systems on a single platform to reduce product costs are gaining considerable interest from different embedded domains [14]. For example, the market for high function in-vehicle technology has experienced a rapid growth. New car functionality may include satellite navigation, road information, entertainment systems or Internet connectivity. In addition, parking and driving aid systems use the information provided by those applications to cooperate with control systems for the steering gear or the engine [16].

In order to develop high-level applications (e.g., a web browser or media player) efficiently, a general-purpose operating system (GPOS) with a high level of functionality is usually essential. However, most GPOS are not able to satisfy the strict requirements of real-time control systems in terms of security, reliability and determinism [15]. For instance, security holes are discovered continuously in GPOS such as Windows or GNU/Linux [17]. For that reason, different solutions that execute a real-time operating system (RTOS) in parallel with a GPOS have been proposed.

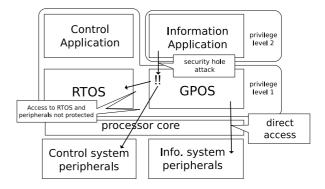

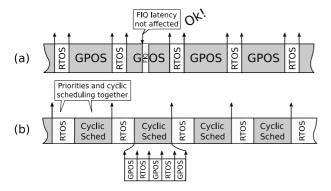

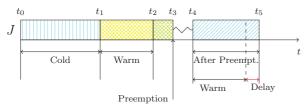

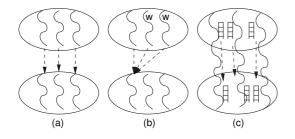

In *hybrid kernel* methods [22, 21] both operating systems execute in privileged level with direct access to the hardware as shown in Fig 1. Although they have the ad-

Figure 1: Hybrid kernel method

vantage of achieving very low overhead, there is no hardware protection between them, and the RTOS can therefore be threatened by a malicious attack or misbehavior of the GPOS. For example, if the GPOS runs out of control with interrupts disabled, the RTOS would not be able to recover control. Furthermore, the GPOS may access memory assigned to the RTOS, causing its failure or stealing sensitive information.

*Virtual Machine Monitor* (VMM/hypervisor) methods [15, 8, 9, 24], on the other hand, provide strong isolation among multiple guest operating systems by executing them under a lower privilege level. The disadvantages of these methods are typically the additional execution overhead caused by privileged instruction emulation; the modifications needed on the guest operating systems [20]; and the loss of isolation caused by DMA capable devices [19]. Fortunately, some embedded processor architectures have recently introduced hardware extensions that facilitate the process of virtualization [23].

A virtualization architecture designed for real-time embedded systems must use a deterministic scheduling algorithm. In some approaches both operating systems are scheduled as black boxes using fixed cyclic scheduling [9]. The main problem with this method is that the worst case response time of the RTOS's activities depends on the size of the slot assigned to the GPOS. This is especially a problem for RTOS interrupts that require short response times. In many other approaches, the GPOS is only executed when the RTOS becomes idle [13, 24]. This method allows the RTOS to take precedence over the GPOS and thus maintain its determinism and low response times. However not all RTOS tasks require the same degree of responsiveness [22], and some GPOS applications and interrupt handlers, such as multimedia on mobile wireless devices, require a certain quality of service [18].

This paper presents a dual operating system virtualization architecture that supports integrated scheduling to enhance the responsiveness of the GPOS while preserving the determinism of the RTOS. The proposed approach takes advantage of common embedded security hardware (ARM TrustZone<sup>®</sup>) to improve the reliability and isolation of the RTOS with low overhead and no modifications to the GPOS core.

The paper is organized as follows. Sec. 2 introduces, briefly, the ARM TrustZone capabilities. Sec. 3 outlines the set of requirements that must be satisfied by the presented architecture, whose design, implementation and evaluation are explained in Sec. 4, 5 and 6. Finally, Sec. 7 draws some conclusions and discusses future work.

## 2. ARM TrustZone

This section briefly introduces the ARM TrustZone<sup>®</sup> security extensions that will be used for the presented virtualization architecture. For more information, refer to [4, 5].

#### 2.1. Trust vs. Non-Trust concept

ARM processors define two privilege levels. In privileged mode, all the system resources can be accessed. On the other hand, in user mode, access to resources is restricted. In a GPOS, the kernel usually runs in privileged mode while applications run in user mode. TrustZone is orthogonal to privilege levels, adding the so-called *Trust* and *Non-Trust* states.

Trust state provides similar behavior to existing privileged and user mode levels. On the other hand, code running under Non-Trust state, even in privileged mode, cannot access memory space (including devices) that was allocated for Trust state usage, nor can it execute certain instructions that are considered critical.

In order to control the TrustZone state, a new mode, called Secure Monitor mode, has been added to the processor. Switching between Trust and Non-Trust state is performed under Security Monitor mode. As a general rule, code in Security Monitor mode runs with interrupts disabled to avoid registers being overwritten when an interrupt arrives.

MMU registers and part of the control registers are banked. When switching the TrustZone state, only general purpose registers that are not banked need to be saved. TrustZone is also supported by the caches to avoid flushing the cache when switching between both states. These features are important for reducing the overhead of switching between Trust and Non-Trust states.

#### 2.2. Address space partitioning

In TrustZone, the address space is divided between regions only accessible in Trust state (Trust area) and regions accessible from both states (Non-Trust area).

When the processor core accesses the bus, a signal indicates the current state (Trust/Non-Trust). Bus controllers

and devices can use that signal to determine the state from which the access was performed. The TrustZone protection controller [3] can be used to configure different regions of memory as Trust or Non-Trust space.

#### **2.3.** Interrupts

In the ARM processor, there are two types of interrupt signals: FIQ and IRQ. When a FIQ or IRQ is generated, the execution is suspended and the program counter is loaded with the address of the corresponding interrupt vector. In TrustZone, there are independent interrupt vectors for the Trust and Non-Trust state. If an interrupt occurs while executing in Trust state, the Trust state vector will be executed, and vice versa. In addition, Secure Monitor mode has its own vector table. It is possible to configure whether FIQ and IRQ are handled by the Trust/Non-Trust vectors, or by the Secure Monitor vectors.

In ARM processors, FIQ and IRQ interrupts can be disabled separately. With TrustZone, it is possible to prevent the Non-Trust side from disabling FIQ interrupts (IRQs can be disabled). For this reason, it is recommended to use IRQs for the Non-Trust state, and FIQs for the Trust state. Distribution of interrupts between both states can be done through the TrustZone Interrupt Controller [2].

## 3. VMM requirements

The following set of requirements were specified for the presented VMM architecture, taking into account the needs of different embedded domains, such as car navigation systems, mobile phones and machine tools.

- (a) Support concurrent execution of a GPOS and an RTOS on an ARM TrustZone single processor.

- (b) Spatial isolation of the RTOS. GPOS failures cannot spread to the RTOS.

- (c) Time isolation of the RTOS. The real-time deterministic behavior of the RTOS must not be affected by the GPOS.

- (d) Support integrated scheduling of the GPOS soft realtime tasks and interrupts.

- (e) Basic mechanisms for device sharing. No overhead must be introduced for devices that are not shared.

- (f) Mechanisms to implement a health monitoring system at the RTOS to monitor the GPOS.

- (g) No modifications to the GPOS core (i.e., dispatcher or interrupt handling code) are required. On the other hand, changes to the RTOS are allowed due to its lower scale.

- (h) The TrustZone monitor implementation must have an execution time smaller than the RTOS interrupt latency.

- (i) The code of the TrustZone monitor implementation must be small and easy to verify.

As shown by requirement (a), the goal of this research is to build a dual operating system architecture, based on security hardware extensions, on a single low-cost processor. Support for multi-processor architectures is planned for future research. Requirement (b) is specified due to the difficulty of increasing the reliability level of a GPOS to the one of a lower size RTOS.

Requirement (c) is specified because systems controlled by the RTOS have stricter real-time requirements than the GPOS processing, while time-consuming tasks such as route searching are better handled by the GPOS. The worst case interrupt response time of the RTOS must be independent of the length of the maximum critical section of the GPOS.

Requirement (d) is specified because some GPOS applications (e.g., multimedia) require a certain quality of service. Integrated scheduling methods to improve the responsiveness of the GPOS without affecting the determinism of the RTOS are desired.

Requirement (e) is related to device sharing. For example, typical devices in a car navigation system include a display, storage disk, in-vehicle network (CAN), timers, to name a few. Not all devices need to be shared. For example, the display is usually able to allocate a frame buffer for each OS, where the RTOS frame buffer has preference over the GPOS buffer. Also, CAN is only used by the control system and each OS has an independent timer device. It is preferable that the use of virtualization does not introduce additional overhead to the operation of devices which do not need to be shared. The hard disk is an example of a device that may require sharing, because the RTOS may need to store critical data. In this study only the basic mechanisms to share a device between Trust and Non-Trust are investigated, leaving for future research a more detailed architecture with a more sophisticated application interface.

An example where requirement (f) is important is a car navigation rear guide application which usually runs on the GPOS. If the image displayed becomes frozen due to some problem, there is a high risk of collision. For that reason, the process of updating the image may need to be monitored from the RTOS. If the GPOS application suffers a failure, a system at the RTOS could be instructed to take the appropriate measurements. The infrastructure for developing a health monitor application that has been investigated in this study includes low-level mechanisms for monitoring the status of the GPOS and its interrupts and an interface to stop, reset and resume the operation of the GPOS.

Regarding requirement (g), in order to run two operating systems simultaneously on a single processor, changes on each of those operating systems might be inevitable. When changes are performed on a large scale, software verification becomes very difficult. In addition, the maintenance of such modifications on different versions of the GPOS usually requires a considerable engineering effort. Therefore changes in the GPOS must be minimized. On the other hand, the RTOS has a lower scale, and so changes are allowed.

Requirement (h) is a performance requirement. The introduction of a TrustZone monitor causes overhead in the interrupt handling due to the necessity to switch between both operating systems. This overhead needs to be as small as possible.

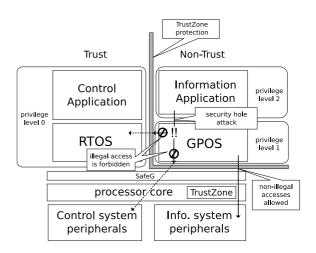

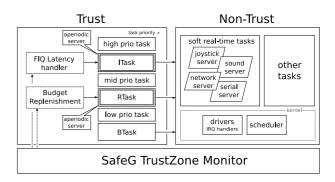

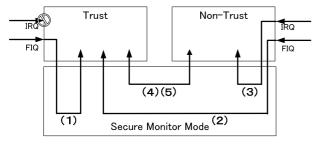

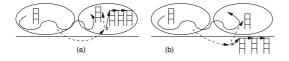

Figure 2: VMM based on TrustZone

Finally, requirement (i) is specified because the Trust-Zone monitor is the cornerstone of the presented architecture. If its reliability is deteriorated, the whole system reliability will be affected. Some important factors for its verifiability are the number of tests required to cover all its possible execution paths, and the size of its code for review.

#### 4. VMM architecture

This section describes the virtualization architecture proposed in this paper, which has been designed with the previous requirements in mind.

#### 4.1. TrustZone configuration

The overall organization of the system is depicted in Fig. 2. To satisfy requirement (a), a TrustZone Monitor called SafeG (Safety Gate) has been designed to execute in Secure Monitor mode and handle the switching between the GPOS, executed in Non-Trust state, and the RTOS, executed in Trust state. The implementation of SafeG is described in Sec. 5.1.

Spatial isolation (requirement (b)) is supported by configuring resources (memory and devices) used by the RTOS to be accessible only from Trust state. The remaining resources are configured to be accessible both from Trust and Non-Trust state. This configuration is performed at initialization time after SafeG is loaded. If the GPOS tries to access some resource configured as Trust space, an exception occurs and SafeG is called.

Time isolation of the RTOS (requirement (c)) is supported by carefully using the two types of interrupt. FIQ interrupts are forwarded to the RTOS, while IRQ interrupts are forwarded to the GPOS. In Trust state, IRQs are disabled so that the GPOS cannot interrupt the execution of the RTOS. For that reason, the GPOS can only execute once the RTOS makes an explicit request, through a Secure Monitor Call (SMC), to SafeG. On the other hand, during the GPOS execution, FIQs are enabled so that the RTOS can recover the control of the processor. TrustZone is configured to prevent the Non-Trust side from disabling FIQ interrupts.

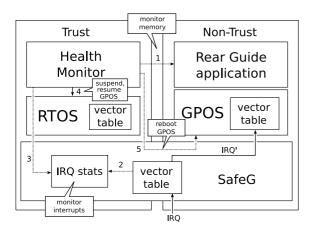

Figure 3: Health monitoring mechanisms

#### 4.2. Support for health monitoring

Some useful mechanisms for requirement (f) include the ability to monitor, suspend, resume and restart the operation of the GPOS. Fig. 3 shows the health monitoring mechanisms in the presented architecture. Monitoring the GPOS status from the RTOS (access 1) is possible because the GPOS resides in Non-Trust space memory, which is accessible from Trust state. To support GPOS interrupt monitoring, IRQs are first processed by SafeG, which implements a Secure Monitor mode vector table, before being forwarded to the GPOS. The frequency and inter-arrival time of the GPOS interrupts can be tracked (access 2) and used by a particular health monitor application in the RTOS (access 3). The operation of the GPOS can be suspended or resumed (access 4) using the RTOS application interface, as described in Sec. 4.4.1. In addition, SafeG offers an SMC to reboot (access 5) the GPOS from the RTOS.

#### 4.3. Device sharing

Devices that do not need to be shared are configured to Trust or Non-Trust space and are accessed directly, without any additional overhead. A basic mechanism for sharing the remaining devices has been designed to achieve requirement (e). More refined methods, including a standard interface, are left for future research. The mechanism is based on using an SMC to make a request to the other OS to handle a certain device. For example, the RTOS may need to handle a shared disk to store sensible data while the GPOS needs to make a request which will be verified. In order to transmit the request, the GPOS executes an SMC together with some parameters, for example the address of the buffer with the data to be stored. The SMC call is handled by SafeG which switches to the Trust state. During the switch, SafeG copies the request type and parameters to the RTOS task, see details in Table 1, that made a switch request previously. In addition, SafeG can be configured to force a special exception in the RTOS when immediate processing is desired. The buffers to store or read the associated data must be in Non-Trust memory so that they can be accessed from both operating systems.

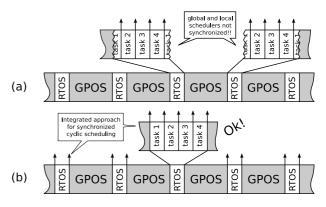

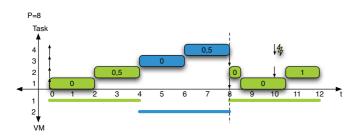

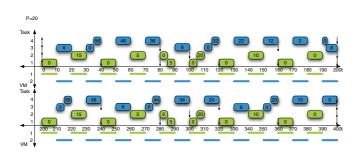

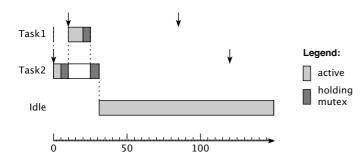

Figure 4: Black box vs Integrated cyclic scheduling

#### 4.4. Integrated Scheduling

#### 4.4.1 The GPOS as an RTOS task

In most VMM architectures, virtual machines are scheduled as black boxes. However, using such a hierarchical scheduling approach, it is difficult to support the integrated scheduling indicated in requirement (d). Furthermore, implementing a new scheduler inside SafeG would complicate its verification, making requirement (h) difficult to satisfy. It would also increase the interrupt latency, since SafeG is executed with interrupts disabled. For that reason, in the presented architecture, the RTOS is used to schedule the GPOS, which is represented as a normal RTOS task. Representing the execution of the GPOS as a fully featured RTOS task gives the user the possibility to use the native RTOS application interface to suspend or resume the operation of the GPOS. This functionality can be used to produce an integrated approach, both for cyclic and priority-based scheduling, and this will be shown in Sec. 4.4.2 and 4.4.3.

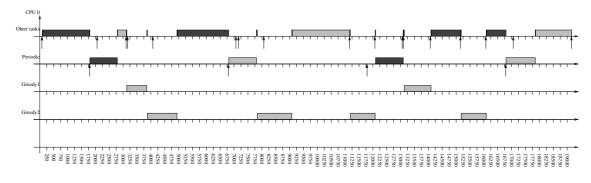

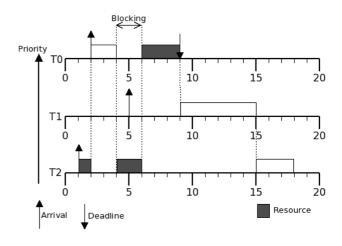

#### 4.4.2 Cyclic scheduling

Cyclic scheduling offers very good determinism properties. Proof of that is the fact that it is used for scheduling virtual machines (partitions) in VMMs aimed at safety critical systems such as spatial systems [9], or in the avionics ARINC 653 standard [1].

One of the problems of cyclic scheduling when applied to dual virtual machines is depicted in Fig. 4 (a). If the RTOS is also based on a cyclic scheduler, it becomes difficult to maintain both the global and internal schedulers synchronized.

In the presented architecture, an integrated cyclic scheduling approach has been implemented. A periodic handler is used, in the RTOS, to suspend and resume the execution of the task associated with the GPOS. With this approach it is easy to produce the synchronized schedule shown in Fig. 4 (b).

Another problem of scheduling virtual machines as black boxes is that the worst case latency of every RTOS operation becomes dependent on the length of the GPOS time slice. This is especially a problem for RTOS interrupts that require a very short response time.

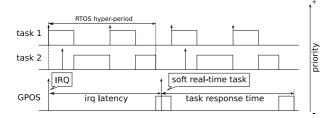

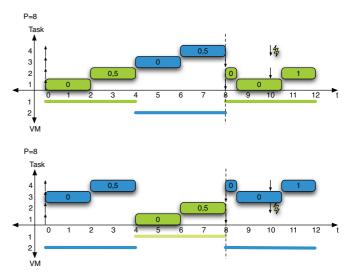

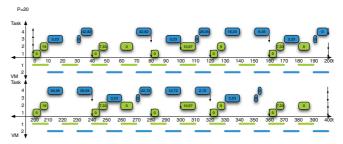

In the presented architecture FIQ interrupts-which are

Figure 5: Latency in integrated cyclic scheduling

Figure 6: GPOS as idle task

assigned to the RTOS and can not be disabled by the GPOS—are able to preempt the execution of the GPOS at any instant. Once the processing of the FIQ handler finishes, the RTOS scheduler resumes the task that was executing (in this example the task representing the GPOS) as shown in Fig. 5 (a). Furthermore, RTOS tasks that require short latency can be scheduled at a priority higher than the whole cyclic schedule as shown in Fig. 5 (b). Another advantage of the presented architecture is that the period and length of the time slice associated with the GPOS can be easily modified at run-time with standard application-level function calls. Furthermore, idle times inside the time slots associated to the RTOS can be easily used to execute the GPOS by creating a new task representing the GPOS at a lower priority.

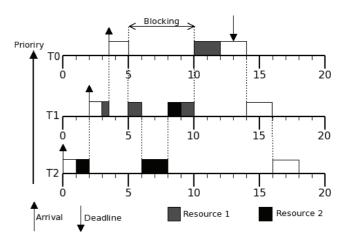

#### 4.4.3 Priority based scheduling

In many other VMMs oriented to real-time systems, the GPOS is only executed when the RTOS becomes idle [13] [24]. This method allows the RTOS to take precedence over the GPOS and thus maintain its determinism. In the presented architecture, this is easy to achieve by configuring the task representing the GPOS processing as the lowest priority task of the RTOS. However, Fig. 6 highlights the problem of using the lowest priority thread to schedule the GPOS. In the figure, an IRQ request in the GPOS is delayed until all the processing at the RTOS is finished. In the worst case, the IRQ request will be attended only after a hyper-period in the RTOS schedule. The latency that can be achieved with this method may not be enough for certain devices. The same situation can happen for the GPOS soft real-time tasks which require a certain quality of service to work correctly.

In order to solve this problem without modifying the

Figure 7: Integrated scheduling architecture

GPOS core (to satisfy requirement (g)) the architecture depicted in Fig. 7 has been implemented. The execution of the GPOS is now handled through several RTOS tasks. In addition to the lowest priority task *BTASK* (Background Task), the *ITASK* (Interrupt Task) is used to enhance the latency of GPOS interrupts, and the *RTASK* (Real-Time Task) is used to improve the quality of service of GPOS soft real-time tasks. The body of the three tasks is the same. The main difference between them is the priority level at which they execute and the way in which they are activated.

The RTASK task is executed at a middle configurable priority, between the BTASK background priority and the priority of the ITASK task. It is necessary that RTOS tasks with lower priority do not suffer starvation or deadline misses. In order to achieve this time isolation (as specified in requirement (c)) the RTASK task runs under the control of an aperiodic server with a configurable period and budget. When the RTASK consumes all the capacity allocated for it, it is suspended. Once it receives new capacity through a budget replenishment it is resumed again. The period and budget of the aperiodic server can be configured to provide a certain quality of service to the GPOS soft realtime tasks. For example, it makes it possible to guarantee that the GPOS will receive an amount of processing time which is equal to its budget for every server period.

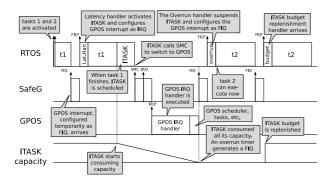

The ITASK task also runs under the control of an aperiodic server but at a higher priority and with a different activation scheme. GPOS interrupts that require short latency are configured temporarily as FIQ interrupt sources and processed by a special handler, called FIQ Latency handler, at the RTOS. Fig. 8 depicts the timeline of an ITASK task activation. Here SafeG processing overhead is included for completeness. When a GPOS interrupt occurs the Latency handler activates the ITASK task and forwards further interrupt requests to the Non-Trust side, as IRQs, by configuring the TrustZone Interrupt Controller. When the ITASK task is scheduled (i.e., when it is the active task with the highest priority) a switch to the Non-Trust state is performed through SafeG, and the GPOS interrupt handler executes. This method makes it possible to represent certain GPOS interrupts through a task with high priority, and so their latency can be enhanced. In the presented architecture, modifications to the GPOS core are avoided (requirement (g)), and therefore the budget of the ITASK task is completely consumed each time a Non-Trust interrupt is

**Figure 8:** ITASK activation timeline (priority: t1 > ITASK > t2)

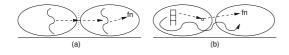

Figure 9: SafeG execution paths

processed. More refined methods that preserve the budget between interrupt instances can be implemented. However, they may require small modifications to the GPOS core in order to return the control back to the RTOS, once the interrupt is served, and therefore they are left for future research.

#### 5. VMM implementation

The implementation of the presented architecture includes the SafeG TrustZone Monitor, the RTOS and the GPOS. TOPPERS/ASP was chosen as the RTOS and Linux as the GPOS.

#### 5.1. SafeG TrustZone Monitor

SafeG is the implementation of the TrustZone Monitor for the presented architecture. It runs in Secure Monitor mode with interrupts disabled. Fig 9 shows the five possible execution paths in SafeG that are necessary to provide the means to switch between both operating systems and handle interrupts. As described in Sec. 4.2, interrupts are captured by SafeG before being forwarded to the appropriate operating system. In order to satisfy requirement (g), it is necessary that the GPOS interrupt entry is not modified. For that reason, SafeG adjusts the value of the registers to appear as if the interrupt had occurred directly, before loading the program counter with the GPOS interrupt vector address. The same procedure is used for RTOS interrupts.

The execution path (1) in Fig 9 shows the path when a FIQ occurs while the RTOS is executing in Trust state. The execution flow is suspended and the SafeG FIQ handler is executed. SafeG FIQ handler performs the necessary processing and jumps to the RTOS interrupt handler.

The execution path (2) shows the path when an FIQ oc-

curs while the GPOS is executing in Non-Trust state. The execution flow is suspended and SafeG FIQ handler performs a context switch. More in detail, 38 GPOS general purpose 32-bit registers are saved in Trust memory and replaced by the corresponding 38 RTOS general purpose registers, the context. After that, the RTOS interrupt handler is called in a similar way as in path (1).

The execution path (3) shows the path when an IRQ occurs while the GPOS is executing in Non-Trust state. The execution flow is suspended and SafeG IRQ handler is invoked. SafeG IRQ handler performs the necessary processing (e.g., interrupt frequency monitoring) and jumps to the GPOS IRQ vector handler.

The execution paths (4) and (5) show the paths when a Secure Monitor Call (SMC) is executed by one of the operating systems. Registers are used to indicate the request type (i.e., switch, message or reboot) and pass arguments when required. When a *switch* request is performed, SafeG saves the context of the calling operating system and loads the context of the other operating system. *Message* requests can be used for device sharing as mentioned in Sec. 4.3, or for other types of intercommunications using Non-Trust memory, to place the associated data. In addition, SafeG can be configured to force an artificial exception in the RTOS, when a message is received, for synchronization purposes.

#### 5.2. RTOS porting and extensions

The TOPPERS project [11] follows the ITRON standard for real-time operating systems to produce high quality open-source software for embedded systems. ASP (Advanced Standard Profile kernel) is one of TOPPERS realtime kernels and is based on the  $\mu$ ITRON4.0 [7] specification with several extensions.

For the purpose of this study, ASP has been ported to an ARM TrustZone-enabled platform (PB1176JZF) to run concurrently with a GPOS (Linux). The porting allows execution in Trust and Non-Trust states as two different target platforms. The porting includes support for:

- Trustzone Interrupt Controller [2].

- Non-Trust Generic Interrupt Controller.

- TrustZone-enabled Memory Management Units.

- FIQ and IRQ interrupt routines with nesting.

- Exception handlers (i.e., data abort, SWI, undefined).

- Dispatcher and context switch code.

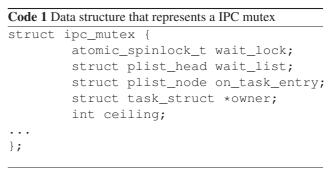

In order to schedule the GPOS mentioned in Sec. 4.4.1, an RTOS task whose body is a loop executing the function shown in Table 1 is used. The function consists of an SMC instruction plus the address of a buffer. A while instruction is used because when the GPOS execution is preempted by an RTOS FIQ and then the task is resumed, the SMC instruction must be executed again. An approach [13] such as modifying the link register value to point to the SMC instruction could be an alternative. However, using the mechanism shown in Table 1, the GPOS is also able to pass requests to the RTOS which can be used as an intercommunication mechanism or to share devices as mentioned in Sec. 4.3. To implement the cyclic scheduling approach pro-

Table 1: ITASK, RTASK and BTASK function body

```

ret_args->arg0 = NULL;

while (1) {

Asm("mov r0, %0\n\t"

"smc %1\n\t"

:: "r" (ret_args),

"I" (NT_SMC_SWITCH)

: "r0", "memory");

if (ret_args->arg0 != NULL)

return;

}

```

posed in Sec. 4.4.2,  $\mu$ ITRON4.0 cyclic handlers are used to suspend (sus\_tsk), resume (rsm\_tsk) or change the priority (chg\_pri) of the GPOS processing. This is done at application level, and thus the internals of the RTOS do not need to be modified.

To implement a priority-based integrated scheduling approach like that described in Sec. 4.4.3, the ASP kernel has been extended to support execution-time overrun handlers. This mechanism makes it possible to limit the processor time of a specific task, and it has been used to implement deferrable servers [12] at application level without modifying the ASP scheduler. Cyclic handlers are used for the budget replenishments.

#### 5.3. GPOS modifications

In the presented VMM architecture the following items may require modifications to the GPOS. No modifications to the core (i.e., scheduler or interrupt handlers) of the GPOS kernel were required.

#### 5.3.1 Vector table

In the ARM processor, it is possible to select a normal vector table which starts at 0x0 or a high vector table starting at 0xFFFF0000. SafeG uses a normal vector table. If the GPOS uses the normal vector table, the GPOS vector table must be stored at a position different to 0x0, and the base address must be written to the vector base address register. In the evaluation environment, Linux was configured to use the high vector table to prevent conflicts with SafeG vector table, and thus no changes are required.

#### 5.3.2 Memory and devices allocation

Memory and devices must be allocated either to Trust or Non-Trust space. To achieve this, it is necessary to modify the GPOS hardware configuration file for a specific platform. If a single device wants to be shared by the RTOS and the GPOS, the application libraries need to be modified to make a request to the RTOS through SafeG.

## 6. Evaluation

This section shows the evaluation of the presented architecture on a real machine. The evaluation platform is a PB1176JZF-S board, equipped with a TrustZone enabled ARM1176jzf processor. The core clock frequency is 210Mhz and it has 32KB data and instruction caches. TOPPERS/ASP version 1.3.1 was used as the RTOS. For the GPOS, an ARM Linux 2.6.24 kernel was used together with a CRAMFS file-system placed into FLASH memory. Since the GPOS can affect the execution time of the RTOS or SafeG through the cache, the whole cache is flushed before taking each measurement.

#### 6.1. SafeG overhead

In this section, requirement (h) is evaluated. Although the presented architecture does not introduce overhead in memory accesses or normal device operation, SafeG introduces a bounded overhead in interrupt processing and Trust-Zone state switching.

Table 2: SafeG execution time

| Path                                   | WCET       |

|----------------------------------------|------------|

| (1) While RTOS runs FIQ occurs         | $0.7\mu s$ |

| (2) While GPOS runs FIQ occurs         | 1.6µs      |

| (3) While GPOS runs IRQ occurs         | $1.2\mu s$ |

| (4) Switch from RTOS to GPOS           | $1.5\mu s$ |

| (5) Switch from GPOS to RTOS           | $1.7\mu s$ |

| From ASP IRQ vector until IRQs enabled | 5.1µs      |

Measurements for each of the execution paths of SafeG are shown in Table 2. Since execution paths (2), (4) and (5) require TrustZone state switching (save and restore context), their execution time is a little higher than paths (1) and (3). As SafeG makes no assumptions about the RTOS that is running, all the processor registers (38 in this case) need to be saved and restored. It is possible to reduce the overhead further by saving only the necessary registers for a specific configuration. For example, in the presented architecture ASP makes switch requests only under task context, and therefore only registers used by the task need to be saved. This optimization reduces the execution time of paths (2), (4) and (5) by 240ns.

The last row in Table 2 indicates the interrupt latency —which is measured as the time between the ASP interrupt vector handler starts until interrupts are enabled again, just before the interrupt service routine is executed—. This processing takes place inside the core of ASP, is written in assembly with no loops, and consists of several steps: save processor context; nested interrupts handling code; judge the interrupt cause; set the interrupt priority; obtain the address of the interrupt handler; and enable interrupts. After that, the user interrupt service routine is called. The execution time of each path is always smaller than ASP interrupt latency, thus complying with requirement (h).

#### 6.2. SafeG code verifiability

To satisfy requirement (i), SafeG code must be small and have as few forks as possible so that source code review becomes easier. The size of the code and data sections of SafeG, ASP and Linux are shown in Table 3. SafeG occupies a total of 1968 bytes, around 1/60 of the size of ASP, which is small enough for verification purposes. A total of 304 bytes in the .bss section of SafeG corresponds to the area where the context of each operating system is stored.

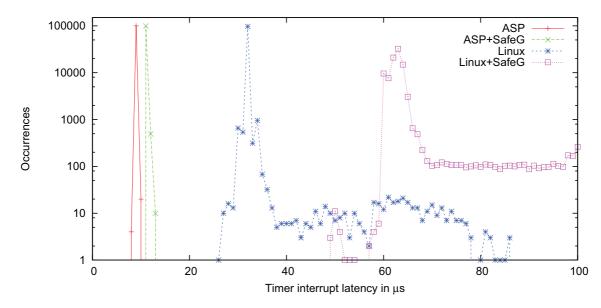

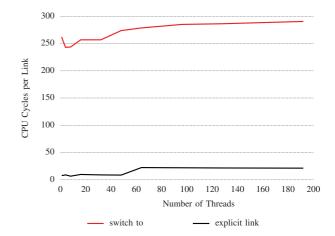

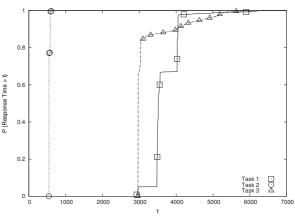

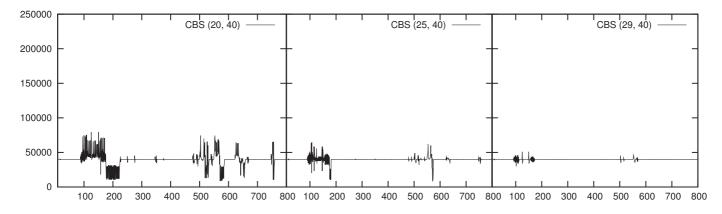

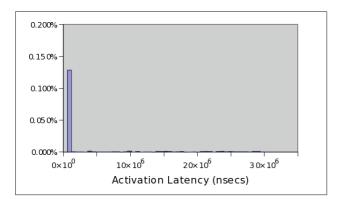

Figure 10: Timer interrupt latency

**Table 3:** Code and data size (in bytes)

|       | text    | data   | bss   | total   |

|-------|---------|--------|-------|---------|

| SafeG | 1520    | 0      | 448   | 1968    |

| ASP   | 34796   | 0      | 83140 | 117936  |

| Linux | 1092652 | 148336 | 89308 | 1330296 |

Inside SafeG there are four forks in total. Three of them occur when SafeG captures an interrupt (IRQ/FIQ) or receives an SMC request. They are required to execute different processing depending on the current TrustZone state. The other fork is required to support instances when a high vector is used, as explained in Sec. 5.3.1. Because there are four forks inside SafeG, only eight types of tests are necessary in order to cover all possible execution paths.

Finally, another factor that helps to satisfy requirement (i) is the fact that SafeG runs with interrupts disabled. If interrupts were enabled, it would be necessary to verify accurately at which point interrupts enter while executing SafeG.

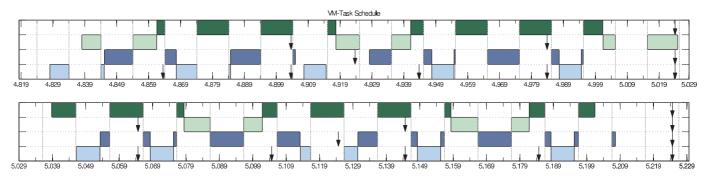

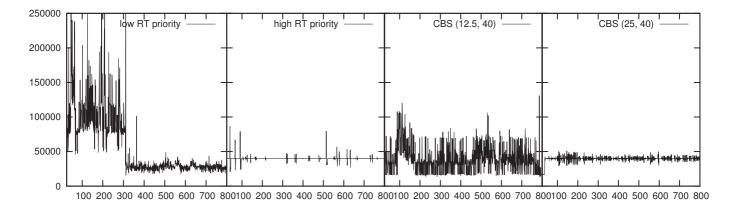

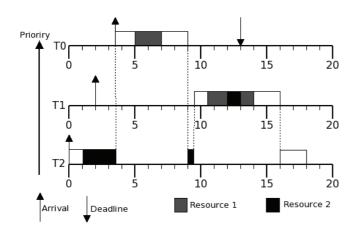

## 6.3. RTOS time isolation

To confirm that RTOS time isolation from the GPOS is satisfied (requirement (c)), the latency of the RTOS timer interrupt is measured before and after the introduction of SafeG. In the RTOS only a periodic operation to renew the system tick is executed every 1ms. The ASP system tick timer is replaced by the ARM performance monitor, whose value is read at the beginning of the timer interrupt service routine, and which contains the cycles corresponding to the interrupt handling code inside ASP. At the GPOS side, a terminal, Xeyes, Xclock and the top command are executed on top of X windows. For completeness, the latency of Linux timer interrupts were also measured.

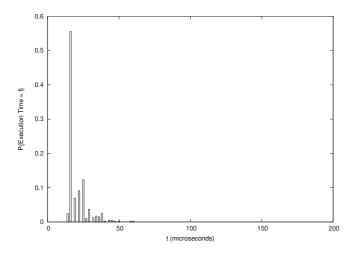

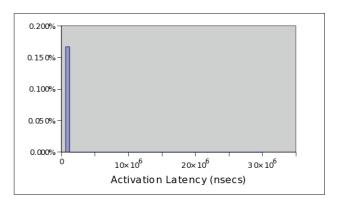

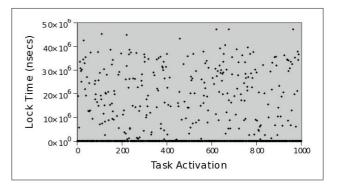

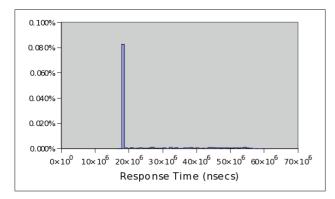

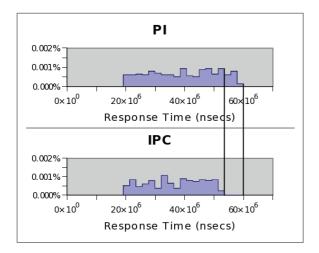

All measurements were repeated for 10,000 times. The results are shown in Fig. 10 where the vertical axis shows the frequency, in logarithmic scale, and the horizontal axis

shows the timer interrupt latencies. As shown in the graph, the introduction of SafeG increased the latency of ASP interrupts by around 2us. This increase is consistent with the values measured for SafeG overhead in Table 2. The worst case occurs when an FIQ interrupt arrives just after SafeG starts switching to the GPOS (with interrupts disabled). Despite the interrupt latency of the RTOS is being increased, it remains bounded and isolated from the GPOS operation, and therefore requirement (c) is satisfied.

The most common measured value of the GPOS timer interrupt latency was incremented by around  $31\mu$ s due to SafeG overhead plus the preemptions caused by the periodic processing of ASP system tick. The worst measured value,  $7637\mu$ s, does not appear in the graph and depends on long critical sections executed with interrupts disabled inside the Linux kernel. This problem is not caused by SafeG and can be addressed with different patches available for the Linux kernel.

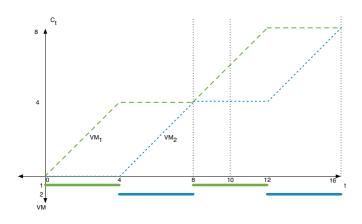

#### 6.4. Integrated scheduling evaluation

This section evaluates whether requirement (d) is satisfied or not with the approach proposed in Sec. 4.4.3.

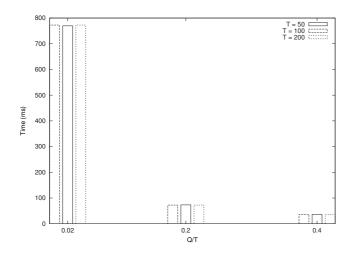

#### 6.4.1 Experiment no. 1: ITASK

In this experiment, the ITASK task shown in Fig. 7 has been assigned to the Non-Trust serial driver interrupt number. The input has been generated randomly by a user who typed characters on the serial console of the Non-Trust operating system at human speed. The *serial driver latency* is measured from the beginning of the FIQ Latency handler until the character is received by the user of the serial driver. Therefore it includes the overhead caused by the architecture, plus the possible blocking times of the RTOS tasks. The RTOS executes two tasks with the parameters shown in Table 4.

Table 5 shows the measured values for three situations.

Table 4: RTOS task parameters

| task | priority | period | duration | utilization |

|------|----------|--------|----------|-------------|

| 1    | high     | 50ms   | 10ms     | 20%         |

| 2    | low      | 300ms  | 100ms    | 33%         |

The first row shows the results when the RTOS tasks from Table 4 are not present. The second row shows the results when using the idle approach. The maximum measured value, 113.9ms, includes the blocking caused by tasks 1 and 2. The last row shows the results when an ITASK task is used at a priority between the two RTOS tasks and with a server period of 30ms and budget of 2ms. The use of the ITASK mechanism reduced the measured latency of the serial port driver to 30.3ms.

**Table 5:** Serial driver latency (in  $\mu$ s)

| approach | min   | avg   | max    |

|----------|-------|-------|--------|

| alone    | 15.7  | 15.81 | 19.47  |

| idle     | 14.6  | 22681 | 113833 |

| itask    | 15.45 | 2292  | 30275  |

Configuring the server with 10ms period gave a maximum latency of 10.3ms caused by the blocking from task 1. However, it is worth mentioning that the shorter the period, the greater the overhead on the RTOS tasks. Non-Trust interrupts assigned to the ITASK task are temporarily handled as FIQs in order to notify the existence of a pending interrupt in the Non-Trust side. A notification takes similar time as a normal interrupt and it is bounded by the server associated to the ITASK task.

#### 6.4.2 Experiment no. 2: RTASK

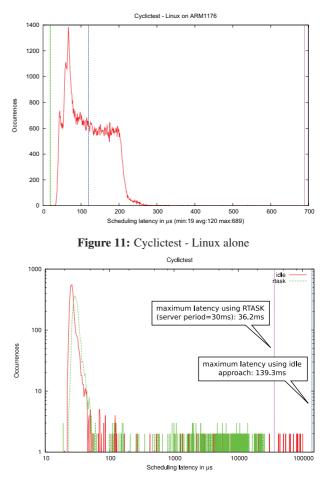

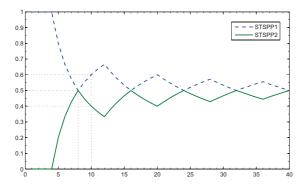

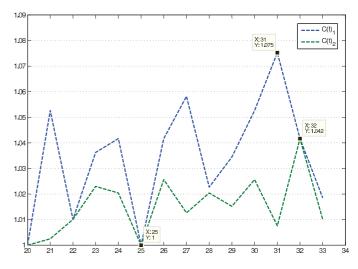

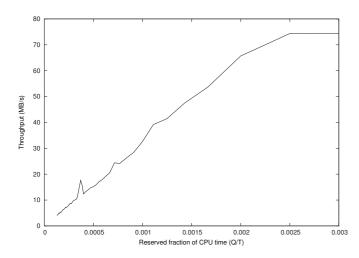

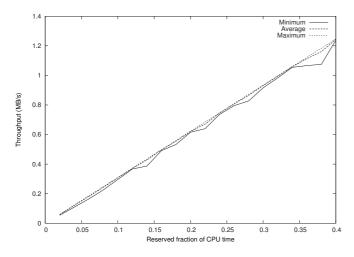

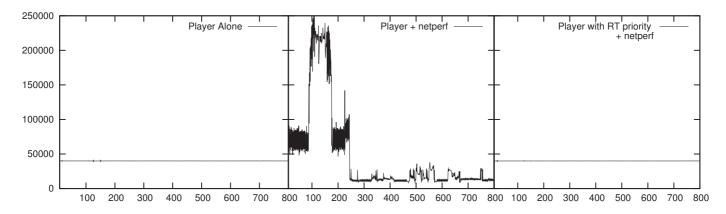

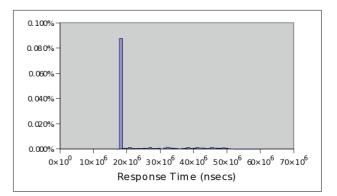

In order to evaluate the effectiveness of the RTASK task for improving the quality of service of soft real-time tasks in the GPOS, the *cyclictest* program [10], has been used to measure the response time of the Linux kernel, which was configured with high resolution timers. This test contains a periodic thread that measures the difference between the instant when a wake up call is scheduled, and then that wake up actually occurs. This measurement includes the interrupt latency, the interrupt service routine duration and the Linux scheduler latency. The program was cross-compiled using Buildroot [6], which was also used to generate a minimal root file-system based on the uClibc C library. It was run for 60 seconds at priority 80, with a single 10ms periodic thread using clock\_nanosleep. In the background, Linux was loaded to use 100% of the CPU.

The test was repeated in three different configurations. Fig. 11 shows the results obtained when Linux is executed alone. Fig. 12 shows the results obtained when the GPOS is executed as the idle task of the RTOS, where they are also compared to those obtained when the GPOS is executed using the architecture described in Sec. 4.4.3. The RTASK task is scheduled through a deferrable server, with period 30ms, budget 5ms and a priority level between the two RTOS tasks. Vertical lines in Fig. 11 indicate the minimum, average and maximum measured values.

As shown in Fig. 11, Linux is capable of obtaining short

Figure 12: Idle vs. RTASK approach

latencies, which is in part thanks to the support for high resolution timers. The worst case measured value in that case was  $689\mu$ s. However, when Linux is executed concurrently with the RTOS and scheduled as the idle thread (Fig. 12) the cyclictest results in a measured maximum latency of 139,3ms. This latency can be explained by the blocking caused by the RTOS task 2 (100ms), plus two or three instances of the RTOS task 1 (10ms each). As Table 6 shows, the maximum measured latency in experiments, which occurs when using an RTASK task with a deferrable server of period 30ms, was reduced to 36,2ms. As the budget and period of the deferrable servers can be configured, the latency of the GPOS soft real-time tasks and interrupts can be adjusted in an integrated scheduling fashion that satisfies requirement (d).

#### 7. Conclusions

In this paper a dual operating system virtualization architecture based on ARM TrustZone<sup>®</sup> was explained and evaluated. Although the natural goal of TrustZone is security, its functionality has been applied to build a VMM architecture that can satisfy the initial requirements shown in Sec. 3. A similar configuration, with some slight differences, was used by [13] but it does not address require-

**Table 6:** Linux kernel latency (in  $\mu$ s)

| approach | min | avg   | max    |

|----------|-----|-------|--------|

| alone    | 19  | 120   | 689    |

| idle     | 22  | 30095 | 139265 |

| rtask    | 19  | 5470  | 36108  |

ments (d), (e) and (f). In addition, no RTOS was ported to the TrustZone platform in that work, and so requirements (a) and (h) were not fully satisfied. The presented approach satisfies all requirements (a)-(i) and has been proven to be appropriate for enhancing the responsiveness of the GPOS, while preserving the determinism of the RTOS, without requiring modifications to the GPOS core.

One possible improvement to increase the usefulness of TrustZone, as a virtualization hardware, could be a mechanism to separate the control of the Trust/Non-Trust caches. Currently, caches are not separated and therefore the Non-Trust side can affect the performance of the Trust side by flushing the cache. Also, when switching from Non-Trust to Trust state there are 38 registers which are not banked, and which need to be saved and restored continuously. The introduction of an instruction for storing and restoring these registers could improve the performance.

As future research, a more refined method for integrating scheduling with small modifications to the GPOS kernel core will be investigated. Device sharing and intercommunications mechanisms using standard interfaces will also be explored. Finally, a porting to new multi-core TrustZoneenabled embedded processors is planned for the immediate future.

#### References

- Airlines Electronic Engineering Committee, 2551 Riva Road, Annapolis, Maryland 21401-7435. Avionics Application Software Standard Interface (ARINC-653), March 1996.

- [2] AMBA3 TrustZone Interrupt Controller (SP890) Technical Overview, DTO 0013B, ARM Ltd., 2008.

- [3] AMBA3 TrustZone Protection Controller (BP147) Technical Overview, DTO 0015A, ARM Ltd., 2004.

- [4] ARM Security Technology. Building a Secure System using TrustZone Technology, PRD29-GENC-009492C, ARM Ltd., 2009.

- [5] ARM1176JZF-S. Technical Reference Manual, DDI 0301G, ARM Ltd., 2008.

- [6] Buildroot. http://buildroot.uclibc.org/.

- [7] H. Takada and K. Sakamura, "µITRON for small-scale embedded systems", *IEEE Micro*, vol. 15, pp. 46-54, Dec. 1995.

- [8] J. Hwang, S. Suh, S. Heo, C. Park, J. Ryu, S. Park and C. Kim, "Xen on ARM: System Virtualization using Xen Hypervisor for ARM-based Secure Mobile Phones", In Proceedings of the 5th Annual IEEE Consumer Communications & Networking Conference, USA, January 2008.

- [9] M. Masmano, I. Ripoll, A. Crespo, and J.J. Metge. "XtratuM: a Hypervisor for Safety Critical Embedded Systems", 11th Real-Time Linux Workshop. Dresden. Germany 2009.

- [10] T. Gleixner cyclictest. https://rt.wiki.kernel. org/index.php/Cyclictest.

- [11] TOPPERS: Toyohashi OPen Platform for Embedded Real-

- Time Systems. http://www.toppers.jp.

[12] G. Bernat and A. Burns. New results on fixed priority aperiodic servers. In 20th IEEE Real-Time Systems Symposium, Phoenix. USA, Dec 1999.

- [13] I. Cereia, M. Bertolotti. Asymmetric virtualisation for realtime systems. In *ISIE 2008*, pages 1680 – 1685, Cambridge, 2008.

- [14] G. Heiser. The role of virtualization in embedded systems. In 1st Workshop on Isolation and Integration in Embedded Systems, pages 11–16, Glasgow, UK, Apr 2008. ACM SIGOPS.

- [15] G. Heiser. Hypervisors for consumer electronics. In CCNC'09: Proceedings of the 6th IEEE Conference on Consumer Communications and Networking Conference, pages 614–618, Piscataway, NJ, USA, 2009. IEEE Press.

- [16] A. Hergenhan and G. Heiser. Operating systems technology for converged ECUs. In 6th Embedded Security in Cars Conference (escar), Hamburg, Germany, Nov 2008. ISITS.

- [17] Y. Kinebuchi, H. Koshimae, S. Oikawa, and T. Nakajima. Virtualization techniques for embedded systems. In Proceedings of the Work-in-Progress Session: the 12th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications, Sydney, Australia, 2006.

- [18] Y. Kinebuchi, M. Sugaya, S. Oikawa, and T. Nakajima. Task grain scheduling for hypervisor-based embedded system. In HPCC '08: Proceedings of the 2008 10th IEEE International Conference on High Performance Computing and Communications, pages 190–197, Washington, DC, USA, 2008. IEEE Computer Society.

- [19] B. Leslie, N. FitzRoy-Dale, and G. Heiser. Encapsulated user-level device drivers in the Mungi operating system. In *Proceedings of the Workshop on Object Systems and Software Architectures 2004*, Victor Harbor, South Australia, Australia, Jan 2004. http://www.cs.adelaide. edu.au/~wossa2004/HTML/.

- [20] J. LeVasseur, V. Uhlig, M. Chapman, P. Chubb, B. Leslie, and G. Heiser. Pre-virtualization: soft layering for virtual machines. Technical Report 2006-15, Fakultät für Informatik, Universität Karlsruhe (TH), July 2006.

- [21] M. Masmano, I. Ripoll, and A. Crespo. An overview of the XtratuM nanokernel. In *1st Intl. Workshop on Oper*ating Systems Platforms for Embedded Real-Time applications. OSPERT 2005, Palma de Mallorca, Spain, Jul 2005.

- [22] H. Takada, S. Iiyama, T. Kindaichi, and S. Hachiya. Linux on ITRON: A Hybrid Operating System Architecture for Embedded Systems. In SAINT-W '02: Proceedings of the 2002 Symposium on Applications and the Internet (SAINT) Workshops, pages 4–7, Washington, DC, USA, 2002. IEEE Computer Society.

- [23] P. Wilson, A. Frey, T. Mihm, D. Kershaw, and T. Alves. Implementing Embedded Security on Dual-Virtual-CPU Systems. *IEEE Des. Test*, 24(6):582–591, 2007.

- [24] S. Yoo, Y. Liu, C.-H. Hong, C. Yoo, and Y. Zhang. Mobivmm: a virtual machine monitor for mobile phones. In *MobiVirt '08: Proceedings of the First Workshop on Virtualization in Mobile Computing*, pages 1–5, New York, NY, USA, 2008. ACM.

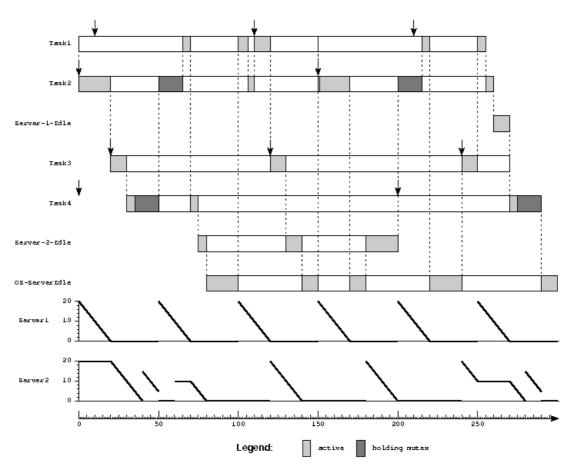

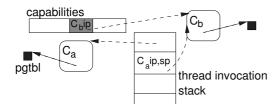

## **Timeslice Donation in Component-Based Systems**

Udo Steinberg Technische Universität Dresden udo@hypervisor.org Alexander Böttcher Technische Universität Dresden boettcher@tudos.org Bernhard Kauer Technische Universität Dresden bk@vmmon.org

Abstract—An operating system that uses a priority-based scheduling algorithm must deal with the priority inversion problem, which may manifest itself when different components access shared resources. One solution that avoids priority inversion is to inherit the priority across component interactions. In this paper we present our implementation of a timeslice donation mechanism that implements priority and bandwidth inheritance in the NOVA microhypervisor. We describe an algorithm for tracking dependencies between threads with minimal runtime overhead. Our algorithm does not limit the preemptibility of the kernel, supports blocked resource holders, and facilitates the abortion of inheritance relationships from remote processors.

#### I. INTRODUCTION

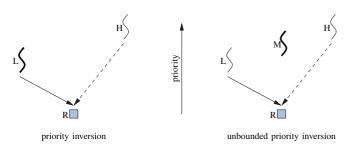

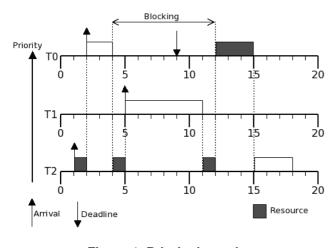

Priority inversion [1] occurs when a high-priority thread H is blocked by a lower-priority thread L holding a shared resource R as illustrated in Figure 1. Priority inversion can be unbounded if a medium-priority thread M prevents the low-priority thread from running and thus from releasing the resource. A lock that protects a critical section from concurrent access is a typical example for a shared resource that can cause priority inversion. In component-based systems the shared resource may also be a server thread that is contacted by multiple clients.

Figure 1. Example of priority inversion: The currently active thread is marked bold.

#### Resource Access Protocols

Several solutions for circumventing the priority inversion problem have been proposed. They range from disabling preemption to using complex protocols to control resource access. Disabling preemption while holding a shared resource is prohibitive in systems with real-time or lowlatency requirements. Protocols such as the priority ceiling protocol (PCP) and the priority inheritance protocol (PIP) [2] avoid priority inversion by defining rules for resource allocation and priority adjustment that guarantee forward progress for threads holding shared resources.

The priority ceiling protocol prevents deadlocks that arise from contention on shared resources. However, PCP requires a priori knowledge about all threads in the system. At construction time every shared resource is assigned a static ceiling priority, which is computed as the maximum of the priorities of all threads that will ever acquire the resource. Priority ceiling is therefore unsuitable for open systems [3] where threads are created and destroyed dynamically or where the resource access pattern of threads is not known in advance. Because priority ceiling relies on static priorities it is not applicable to scheduling algorithms with dynamic priorities, such as earliest deadline first (EDF) [4].

When using the priority inheritance protocol, the priority of a thread that holds a shared resource is temporarily boosted to the maximum of the priorities of all threads that are currently trying to acquire the resource. Priority inheritance works in systems with dynamic priorities and does not require any prior knowledge about the interaction between threads and resources.

Bandwidth inheritance (BWI) [5] can be considered an extension of the priority inheritance protocol to resource reservations. Instead of inheriting just the priority, the holder of a shared resource inherits the entire reservation of each thread that attempts to acquire the resource. Bandwidth inheritance reduces the blocking time for other threads when the resource holder's own reservation is depleted.

Resource reservations in our system are called timeslices and consist of a time quantum coupled with a priority. Timeslices with a higher priority have precedence over those with a lower priority. The time quantum facilitates roundrobin scheduling among timeslices with the same priority.

In this paper, we describe and evaluate the timeslice donation mechanism of the NOVA microhypervisor [6]. This mechanism allows for an efficient implementation of priority and bandwidth inheritance in an open system with many threads. We discuss issues that arise when threads block or unblock while holding shared resources and explore how blocking dependencies can be tracked with minimal overhead.

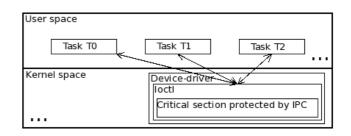

#### II. BACKGROUND

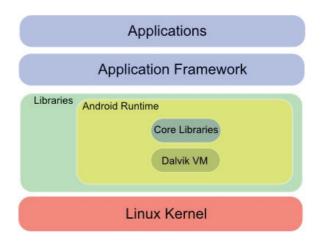

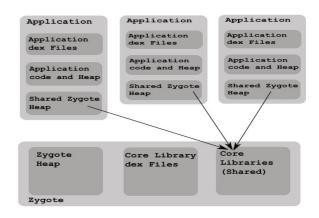

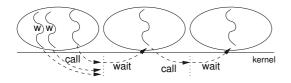

Component-based operating systems achieve additional fault isolation by running device drivers and system services in different address spaces. Communication between these components must use inter-process communication (IPC) instead of direct function calls in order to cross addressspace boundaries. When multiple clients contact the same server, threads in the server are a shared resource and therefore prone to cause priority inversion.

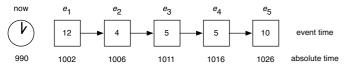

Lazy scheduling was originally introduced as a performance optimization in the L4 microkernel family to bypass the scheduler during inter-process communication [7]. Figure 2 illustrates the communication between a client and a server thread. Because threads and timeslices are separate kernel objects, the kernel can switch them independently. During IPC, the kernel changes the current thread from the client C to the server S and back, without changing the current timeslice. The effect is that the client donates its timeslice to the server.

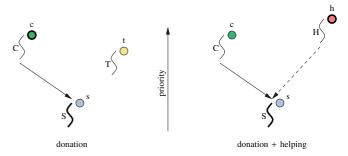

Figure 2. Synchronous communication between a client and a server in a component-based system. Left side: During the request the client thread C donates its timeslice c to the server thread S. Right side: When the server responds, the kernel returns the previously donated timeslice c back to the client.

Timeslice donation can be used to implement priority inheritance, but only if the kernel correctly resumes the donation after a preemption. For this purpose the kernel must track dependencies between threads so that it can determine the thread to which a timeslice has been most recently donated. Most versions of L4 do not implement dependency tracking. Therefore, priority inversion may occur when a server thread is preempted and afterwards uses its own, potentially low-priority, timeslice. This problem is described in more detail in [8].

#### Timeslice Donation and Helping

The NOVA microhypervisor implements priority and bandwidth inheritance using the following two closely related mechanisms:

**Donation:** In the left example of Figure 3, a highpriority client thread C sends an IPC to a low-priority server thread S. By donating the client's timeslice c to the server, the priority of S is boosted to that of C and the kernel can directly switch from the client to the server without having to check for the existence of ready threads with priorities between the client and the server, such as the mediumpriority thread T. Without timeslice donation, S would use its own low-priority timeslice s and T would be able to preempt S, thereby causing priority inversion for C. During IPC, the kernel establishes an explicit donation dependency from C to S, which we denote by a solid arrow. When the scheduler selects the client's timeslice c, it follows the donation dependency and activates S instead of C, thereby resuming the donation.

Helping: Donation boosts the priority of a server to that of its current client and ensures that, for as long as the server works on behalf of the client, it can only be preempted by threads with a higher priority than the client. Helping augments donation by boosting the priority of the server even further when higher-priority clients try to rendezvous with the server while it is busy handling a request. In the right example of Figure 3, the server thread S is handling the request of a client thread C and initially uses the client's timeslice c. Another thread H with a higher priority than Ccan preempt the server and attempt to rendezvous with S. Because the rendezvous fails, H switches directly to S in order to help S finish its current request, thereby elevating the priority of S to that of H. Unlike donation, the kernel does not establish an explicit dependency from H to S. Upon selecting the timeslice h, the scheduler activates H, which simply retries its operation. We denote such an implicit helping dependency by a dashed arrow.

Figure 3. Example of timeslice donation and helping during client-server communication. The currently active thread and timeslice are marked bold.

Threads in a realtime system typically obtain only a limited time quantum in each period of execution. If a server exhausts the time quantum of its current client during the handling of a request, the server becomes stuck until the client's time quantum has been replenished. In such cases other clients cannot rendezvous with the server and therefore make use of the bandwidth inheritance property of the helping mechanism to allow the server to run the request to completion.

Similar issues arise when a client aborts its request before the server can reply, when the client is deleted, or when the communication channel between the client and the server is destroyed. Such cases leave the server in an inconsistent state that is similar to the state when the server is preempted, except that the old client will no longer provide the time quantum for the server to complete the request. Instead, subsequent clients use the helping mechanism to bring the server back into a consistent state where it can accept the

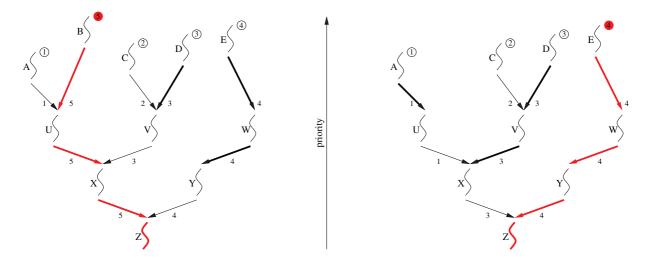

Figure 4. Dependency tracking: The highest-priority incoming edge of each node and the currently active thread and timeslice are marked bold. Changes to nodes in the priority inheritance tree may require updates along the path from the changed node to the root node. In this example the incoming edges of U, X, and Z must be updated when B leaves the priority inheritance tree.

next request. Because synchronous communication between threads on the same CPU always uses timeslice donation and helping, server threads that can only be contacted on their local CPU do not need a timeslice of their own.

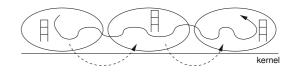

The donation and helping mechanisms are transitive. If a server needs to contact another server to handle a client request, it further donates the current timeslice to the other server for the duration of the nested request. Therefore, the kernel must be able to handle large dependency tracking trees.

#### Multiprocessor Considerations

Helping and donation cannot be easily extended to multiprocessor systems and we are currently aware of only one proposal that describes a multiprocessor priority inheritance protocol [9].

One observation is that priorities of threads on different CPUs are not directly comparable. Additionally, the result of any comparison would quickly become outdated when other processors reschedule. Another observation is that a client cannot donate time from its CPU to help a server on another CPU. Such an operation would cause time to disappear on one processor and to reappear on another. Donating additional time to an already fully loaded CPU causes overload and can potentially break real-time guarantees.

The overload situation can be avoided if the client pulls a preempted server thread over to its CPU to help it locally. However, such an approach requires the address space of the server to be visible and identically configured on all processors on which clients for this server exist. In cases where client threads from different CPUs attempt to help the same server thread simultaneously, the kernel would need to employ a complex arbitration protocol among all helping client threads to ensure that each server thread executes on one processor only at a time. Furthermore, migrating the working set of the server thread to the CPU of the client and then back to the original CPU can result in a significant amount of coherence traffic on the interconnect.

Due to these drawbacks our algorithm does not include cross-processor helping. However, it supports IPC aborts from remote CPUs.

#### III. RELATED WORK

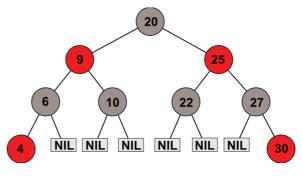

In our previous work on capacity-reserve donation [10], we described an algorithm for computing the effective priority of a server as the maximum of the effective priorities of its current and all pending clients. The algorithm performs the tracking of dependencies and priorities by storing priority information inside the nodes and along the edges of a priority inheritance tree. For each node in the tree, the outgoing edge is marked with the maximum of the priority along all incoming edges of that node as shown in Figure 4.

Unfortunately, changes to nodes of the inheritance tree may require numerous updates to the edges of the tree as shown on the right side. When thread B leaves the priority inheritance tree (because it experiences an IPC timeout or is deleted), the kernel must recompute the priorities along the edges from the changed node down to the root node. In this example, the kernel must update the incoming edges of threads U, X, and Z to determine that the timeslice of thread E has become the highest-priority timeslice donated to Z. Depending on the nesting level of IPC, the number of updates to the priority inheritance tree can become very large, resulting in long-running kernel operations that must be executed atomically. Protecting the whole tree with a global lock for the duration of the update is undesirable because it disables preemption and limits the scalability of the algorithm in multiprocessor environments.

A more efficient version of the bandwidth inheritance protocol [11] has been implemented in the Linux kernel. It also uses a tree structure to track the dependencies between tasks and resources. When a task blocks on a shared resource, all tasks that previously inherited their bandwidth to that task must be updated to inherit their bandwidth to the holder of the shared resource instead.

OKL4 is a commercially deployed L4 microkernel, which is derived from L4Ka::Pistachio. OKL4 tracks IPC dependencies across preemptions and implements a priority inheritance algorithm. The kernel grabs a spinlock during updates to the inheritance tree in order to guarantee atomic updates.

With the realtime patch [12] series, support for priority inheritance was introduced to the Linux kernel. Because the realtime patch made the kernel more preemptible, the need arose to avoid unbounded priority inversion when threads are preempted while holding kernel locks [13]. Further research based on the Linux realtime patches, especially in the context of priority inheritance, is conducted by the KUSP [14] group. Their research focus is on supporting arbitrary scheduling semantics using group scheduling [15] in combination with priority inheritance.

#### IV. IMPLEMENTATION

Dependency tracking algorithms that store priority information along the edges of the priority inheritance tree share the problem that updates to a node in the tree require a branch of the tree to be updated atomically. For example, when a client with a high-priority timeslice joins or leaves an existing priority inheritance tree, it must rewrite the priority information along the edges from the client to the server at the root of the tree as shown in Figure 4. The update of the tree cannot be preempted because the scheduler must not see the tree in an inconsistent state. Therefore, the duration of the update process defines the preemptibility of the kernel. In an open system, a malicious user can create as many threads as his resources permit, arrange them in a long donation or helping chain and then cause an update in the priority inheritance tree that will disable preemption in the kernel for an extended period of time. Therefore, we devised a new dependency tracking algorithm that does not affect the kernel's preemptibility and at the same time keeps the dependency tracking overhead low. Before we describe this algorithm in detail, we present our requirements.

#### Requirements

To prevent malicious threads from being able to cause long scheduling delays in the kernel, we require updates in the priority inheritance tree to be preemptible. Furthermore, we demand that each operation is accounted to the thread that triggered it. Our goal is to move all time-consuming operations from the performance-critical paths in the kernel into functions that are called infrequently. For example, we strive to move as much dependency tracking as possible out of the IPC path into the scheduler and into functions that handle deletion of threads and communication aborts. The new dependency tracking algorithm works for an arbitrary number of threads and is not limited to small-scale systems or systems where all communication patterns must be known in advance.

#### Improved Algorithm for Dependency Tracking

Our new algorithm is based on the idea of storing no priority information whatsoever in nodes of the tree, which obviates the need for updating the priorities when threads join or leave the priority inheritance tree. Furthermore, priority information in the tree cannot become stale. However, this approach requires the kernel to restore the missing information during scheduling decisions, which works as follows:

When invoked, the scheduler selects the highest-priority timeslice from the runqueue and then follows the donation links to determine the path that the timeslice has taken prior to a previous preemption. When the scheduler finds a thread that has no outgoing donation link, it switches to that thread. In the left example of Figure 4, the scheduler selects the timeslice with priority 5, which belongs to thread B, and then follows the donation links from B via U and X to Z. Because Z has no outgoing edge, Z is dispatched. When thread B leaves the tree as shown in the right example of Figure 4, the scheduler selects the timeslice with priority 4, which belongs to thread E and then follows the donation links from E via W and Y to the server Z.

Traversing the donation links from a client's timeslice to the server at the root of the priority inheritance tree is a preemptible operation. If a higher-priority timeslice is added to the runqueue while the scheduler is traversing the tree, the kernel restarts the traversal, beginning with the higher-priority timeslice instead. The benefit of this algorithm is that whenever nodes in the inheritance tree are added or removed, no priority information must be updated. Algorithms that store priorities in all nodes of the tree can quickly determine the highest-priority timeslice donated to a thread by checking the highest-priority incoming edge of that thread. In contrast, our algorithm must compute this information by traversing the priority inheritance tree after a preemption. We quantify the cost for this operation in Section V.

#### Blocking

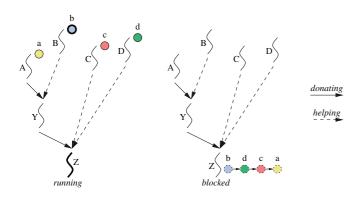

An interesting scenario occurs when the server thread at the root of a priority inheritance tree blocks. This can happen when the server waits for an interrupt that signals completion of I/O or when it waits for the reply from a cross-processor request for which timeslice donation cannot be used.

In the left example of Figure 5, a server thread Z blocks while using timeslice b. In that case the kernel removes b

Figure 5. Blocking of threads when the holder of a shared resource is blocked.

from the runqueue and enqueues it in a priority-sorted queue of timeslices that are blocked on Z. During the subsequent reschedule operation, the scheduler selects timeslice d and traverses the priority inheritance tree down to Z. When it finds that Z is still blocked, d is also added to the queue of blocked timeslices. The right side of Figure 5 illustrates that all other timeslices that have been donated to Z are gradually removed from the runqueue and become blocked on Z when they are selected by the scheduler.

#### Staggered Wakeup

When Z eventually becomes unblocked, all timeslices that have previously been blocked on Z must be added back to the runqueue, effectively reversing the operation of blocking from Figure 5. Because an arbitrary number of timeslices can potentially be blocked at the root of a priority inheritance tree, releasing all of them at once contradicts our requirement of avoiding long scheduling delays. Based on the observation that only the highest-priority timeslice from the blocked queue will actually be selected by the scheduler, releasing the other timeslices can be deferred. The left side of Figure 6 illustrates that, when Z becomes unblocked, the kernel adds b, the highest-priority timeslice blocked on Z, back to the runqueue. The other timeslices that were blocked on Z remain linked to b and are not added to the runqueue yet. When b lowers its priority or is removed from the runqueue, the kernel adds d, the first timeslice linked to b, back to the runqueue and leaves the remaining timeslices linked to d as shown in the right of Figure 6. The benefit of this approach is that when Z unblocks, only a single timeslice needs to be added to the runqueue. The other blocked timeslices will be released in a staggered fashion.

#### Direct Switching

Recall from Figure 2 that the kernel implements timeslice donation by directly switching from one thread to another while leaving the current timeslice unchanged. When a server responds to its client, the kernel must check whether it can undo the timeslice donation by directly switching back

Figure 6. Staggered wakeup of threads when the holder of a shared resource unblocks.

to the client. Switching back to the client is wrong in cases where the server is currently using the timeslice of a highpriority helper and the client and the helper do not share the same incoming edge in the priority inheritance tree of the server. For example, when Z responds to Y in the left example of Figure 5, the kernel can only switch from Z to Y if Z is running on timeslice a or b. If Z is running on timeslice c or d, the kernel cannot return the timeslice to Y, because the timeslice was not donated to Z via Y. The kernel must instead switch to thread C or D so that they can retry their rendezvous with Z. Because our algorithm does not store any information along the edges of the priority inheritance tree, the kernel uses the following trick: When the scheduler selects a new timeslice and starts traversing the tree, the kernel counts the number of consecutive donation links along the path in a CPU-local donation counter. At the beginning of a new traversal and every time the kernel encounters a helping link, the donation counter is reset to zero. The donation counter indicates how often the kernel can directly switch from a server back to its client. When Z replies to Y in the left example of Figure 5, the current timeslice is b and the donation counter is 1, indicating that the kernel can directly switch from Z to Y, but not from Y to A. When a client donates the current timeslice to a server, the kernel increments the donation counter. When a server responds to its client, the kernel decrements the donation counter. The update of the donation counter is the only overhead added to the performance-critical IPC path by our dependency tracking algorithm.

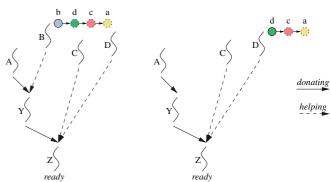

#### Livelock Detection

Communication in component-based systems can lead to deadlock when multiple threads contact each other in a circular manner. In Figure 7, a client thread C contacts a server Y, which in turn contacts another server Z. Deadlock occurs when Z tries to contact Y. In our implementation, Y and Z would permanently try to help each other, thereby turning the deadlock into a livelock.

In NOVA, the kernel can easily detect such livelocks during the traversal of the priority inheritance tree by counting the number of consecutive helping links in a *helping counter*. When the value of the helping counter exceeds the number of threads in the system, the kernel can conclude that the current timeslice is involved in a livelock scenario. It can then remove the timeslice from the runqueue and print a diagnostic message.

Figure 7. Development of a Livelock

#### V. EVALUATION

We evaluated the performance of our priority-inheritance implementation using several microbenchmarks, which we conducted on an Intel Core2 Duo CPU with 2.67 GHz clock frequency.

In contrast to dependency tracking algorithms that store priority information in each node of the inheritance tree, our algorithm keeps the priority information only in the timeslices bound to the client threads that form the leaves of the inheritance tree. Whenever the current timeslice changes, the scheduler must follow the dependency chain to find the server thread at the root of the inheritance tree to which the timeslice has been donated. Fortunately such tree traversals are neither very frequent nor very expensive.

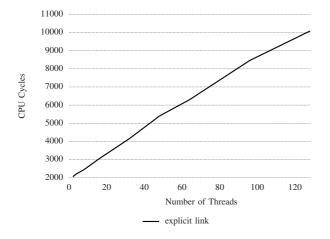

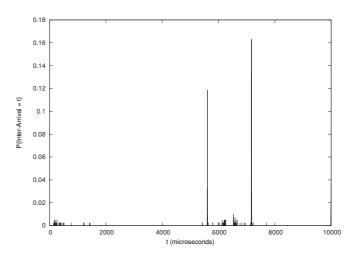

#### Frequency of Dependency Tracking